GEFÖRDERT VOM

Bundesministerium

für Bildung

und Forschung

## TEILVORHABEN

# Technologien der Aufbau- und Verbindungs-technik für Photonik und Mikroelektronik

**Förderkennzeichen: 16ESE0352**

**Laufzeit: 01.05.2019 bis 30.10.2022\***

(\* 6-monatige KN Verlängerung)

im Rahmen des Gesamtvorhabens

## APPLAUSE

**Advanced packaging for photonics, optics and electronics

for low cost manufacturing in Europe**

Call: ECSEL 2018-1 Innovation Action

## Schlussbericht

**Berichtszeitraum: 01.05.2019 bis 31.10.2022**

**Fraunhofer IZM**

|                                                                         |                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Partner:<br><br>Fraunhofer IZM<br>Gustav-Meyer-Allee 25<br>13355 Berlin | Kontaktperson:<br><br>Dr. Charles-Alix Manier<br><a href="mailto:Charles-alix.manier@izm.fraunhofer.de">Charles-alix.manier@izm.fraunhofer.de</a><br>Tel.: +49 30 46403 -612<br><br>Dr. Hermann Oppermann<br><a href="mailto:hermann.oppermann@izm.fraunhofer.de">hermann.oppermann@izm.fraunhofer.de</a><br>Tel.: +49 30 46403 -163 |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

# Schlussbericht

**zum Teilvorhaben:**

## **Technologien der Aufbau- und Verbindungstechnik für Photonik und Mikroelektronik**

**Zuwendungsempfänger: Fraunhofer-Gesellschaft für ihr Institut**

- **Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM**

**Förderkennzeichen: FKZ: 16ESE0352**

**Laufzeit des Vorhabens: 01.05.2019 bis 31.10.2022\* (\* 6-monatige KN Verlängerung)**

**Berichtszeitraum: 01.05.2019 bis 30.10.2022 (ECSEL M01-M42)**

## **Teil I: Zusammenfassung**

### **Aufzählung der wichtigsten wissenschaftlich-technischen Ergebnisse und anderer wesentlicher Ereignisse (maximal 1/2 Seite!).**

Im Lauf des Projektes sind die Arbeiten nach Auslegung von Spezifikationen (WP2) und Design (WP3) mit Projekt-Partners um einzelnen Prozess-entwicklungen (WP4) und Überführung in einer Prozesskette für Packaging (WP5) herum drei anvisierten Applikationen gelenkt worden:

- Applikation 2 - Kostengünstige Wärmebildgeräte,

- Applikation 3 - Passive Faserausrichtung für Single-Mode-Transceiver und

- Applikation 4 - Herzüberwachungssystem

Arbeiten am Fraunhofer IZM auf Prozesse sind in Shortloops und deren Kombinationen in gesamten Prozessabläufen (WP4) durchgeführt worden, um die Überführung in WP5 (Packaging) zu gewährleisten.

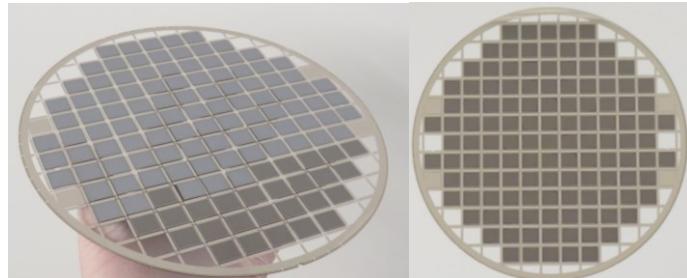

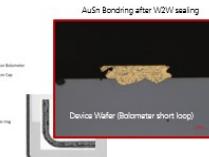

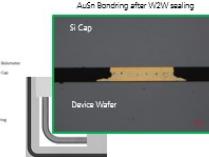

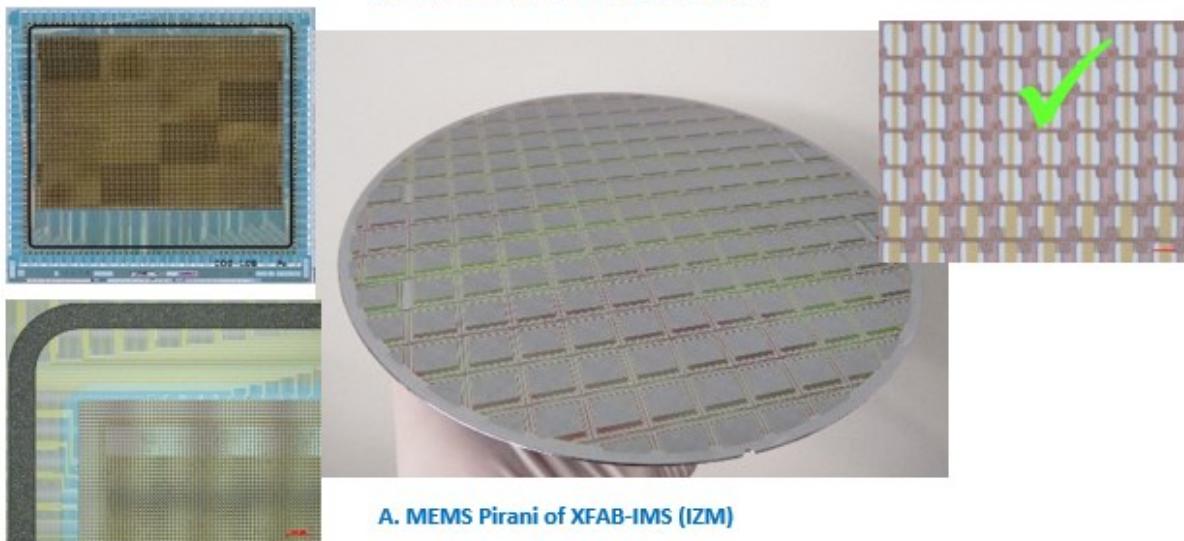

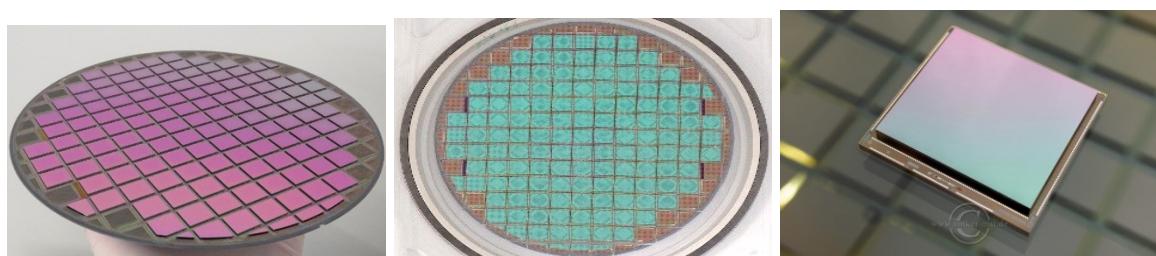

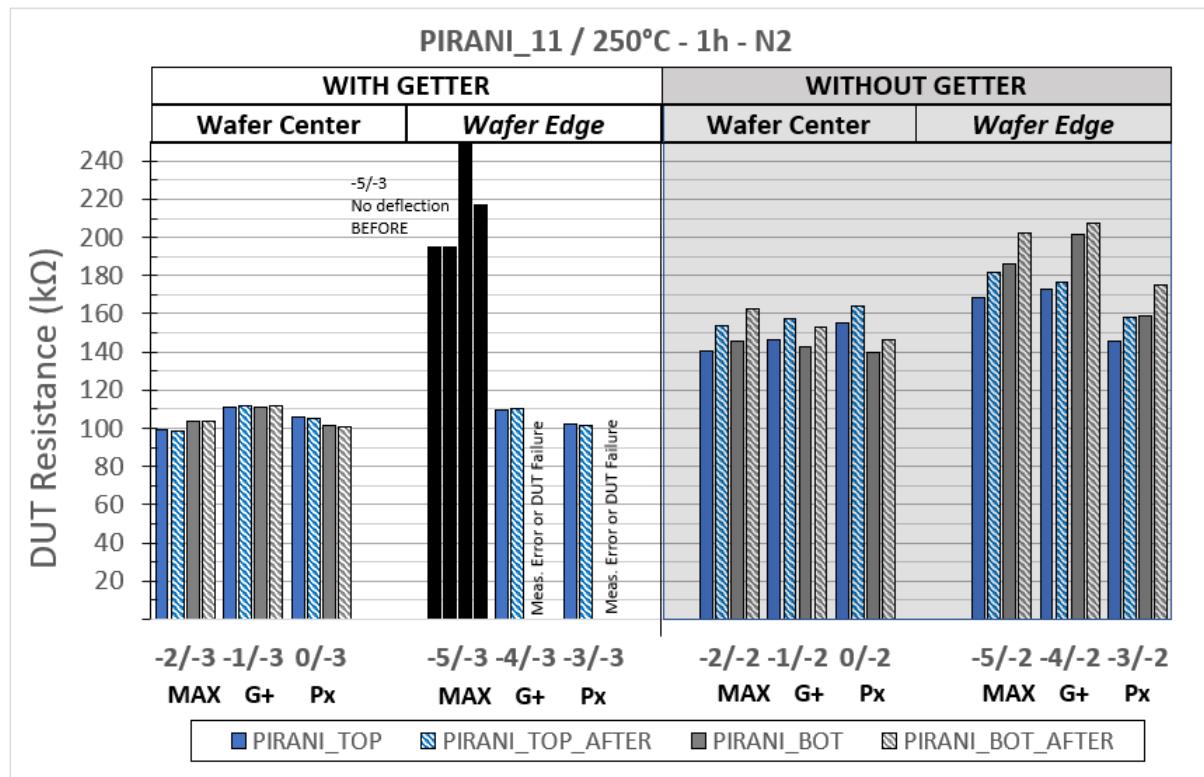

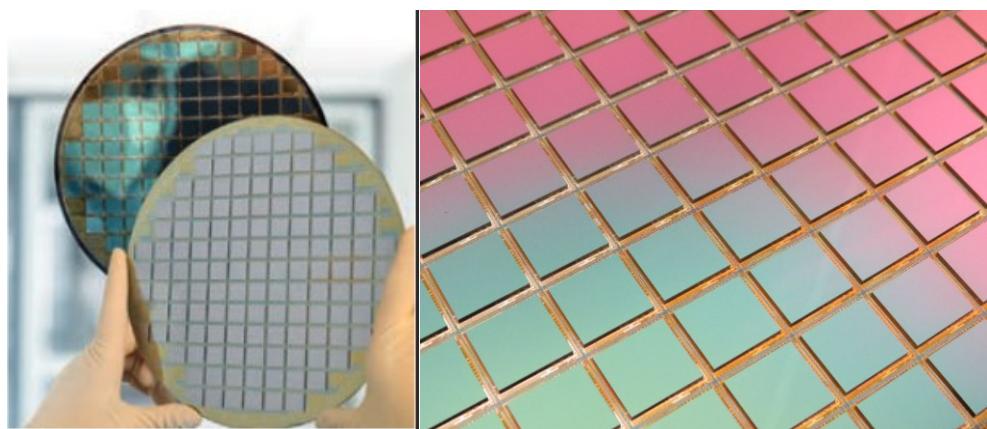

Bei der Applikation 2 sind die Prozessabläufe für die Vorbereitung von Device Wafer (Sensor) und Silizium Cap Wafer (Deckel) vollständig abgeschlossen worden und Packaging führten letztendlich zur Wafer Level hermetischen Verkapselung unter Vakuum sowohl von Mikrobolometer Materialen von der Firma IDEAS (Norwegen) über seinen Partner NNFC (Süd-Korea) bereitgestellt, als auch von MEMS-basierten Pirani Sensoren von Fraunhofer IMS (Fertigung) und USN (Design und Charakterisierung) (University South Norway, Norwegen). Hiermit wurde in 2023 eine Vakuum Level von  $10^{-1}$  mbar nachgewiesen. Die Wafer Level Verkapselung-Ausbeute (Yield) wurde bei über 95% abgeschätzt. Bond-Tests anhand flachen Germanium-Lid auf Silizium-Frame erwiesen sich auf Chip-level nicht zufriedenstellend, mit Teilbruch oder Riss-Bildung in Si-Stegen (Bond auf Silizium Frame) oder in Ge (Bond auf flächigem Si) bei AuSn-Bonden auf Silizium und belegt eine Full-Silicon-Packaging Ansatz als geeigneter für Wafer Level Bonding.

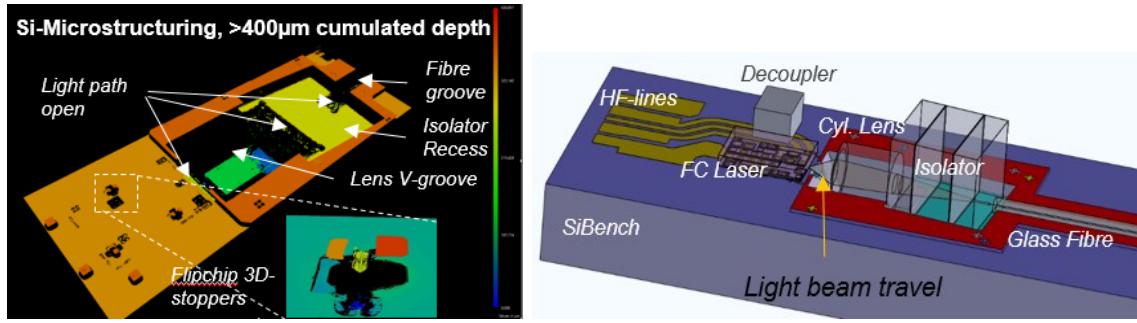

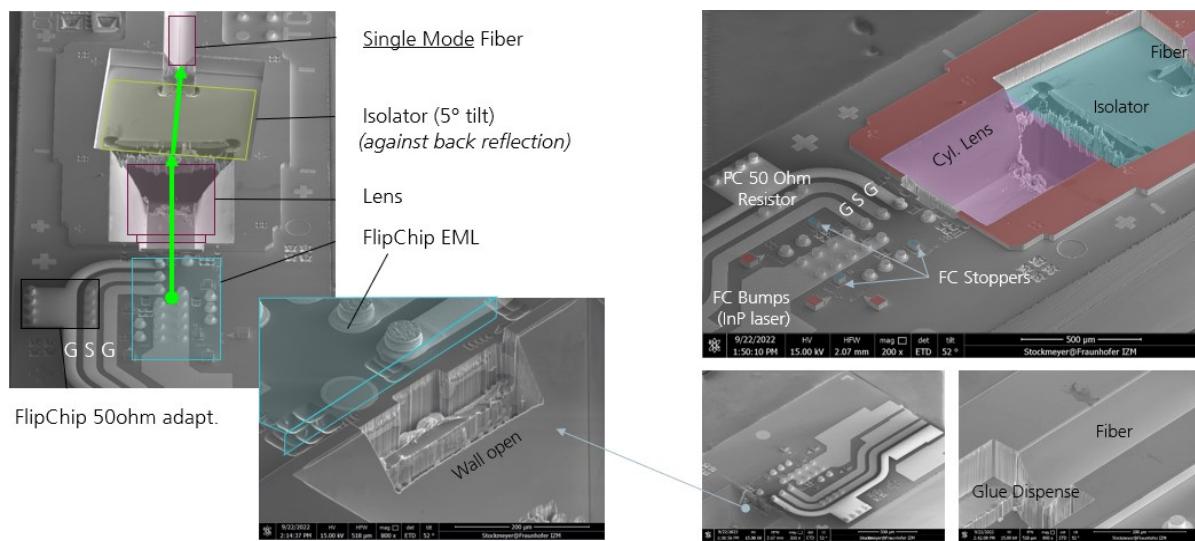

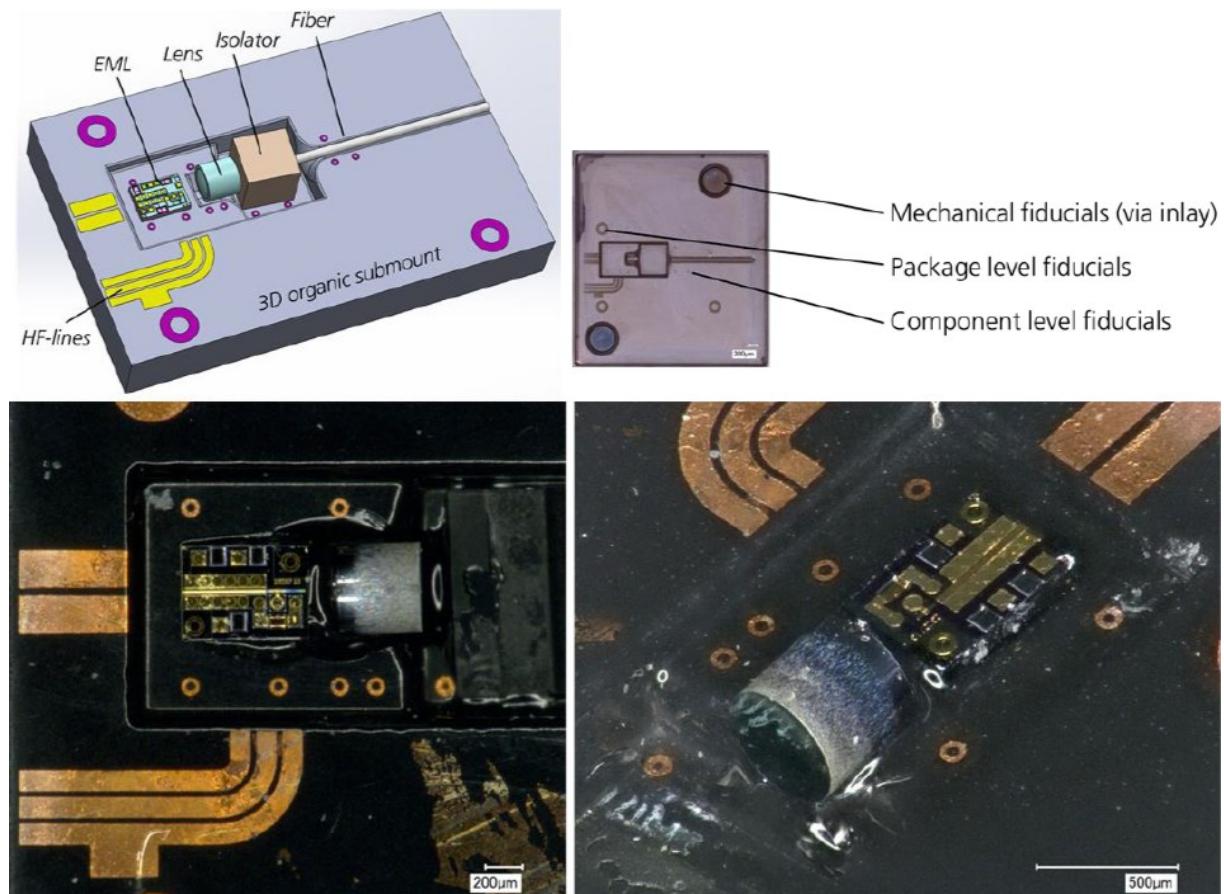

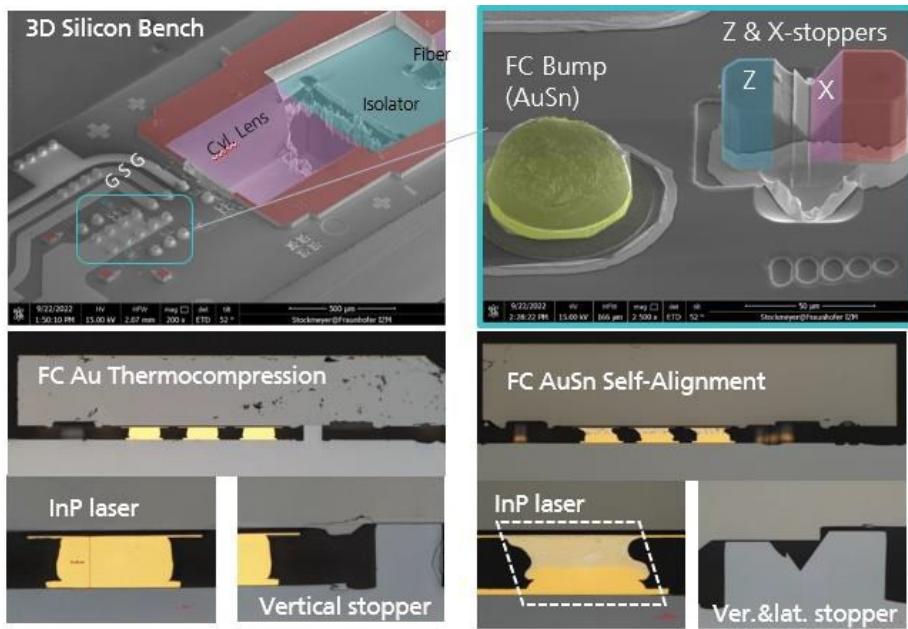

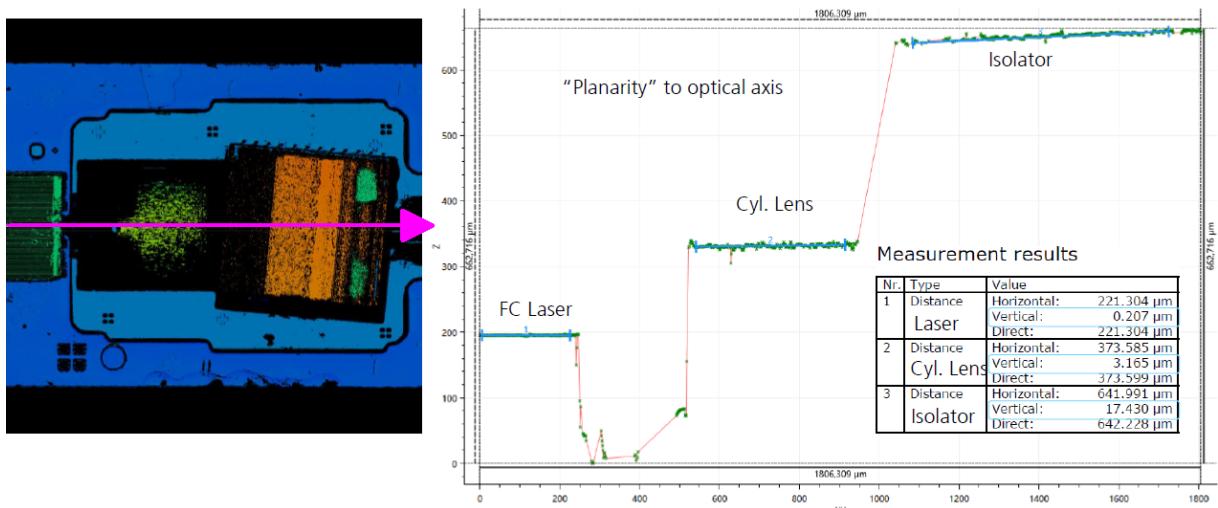

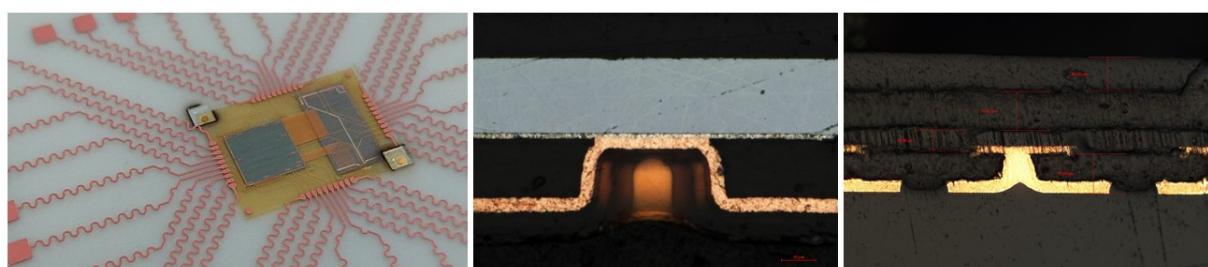

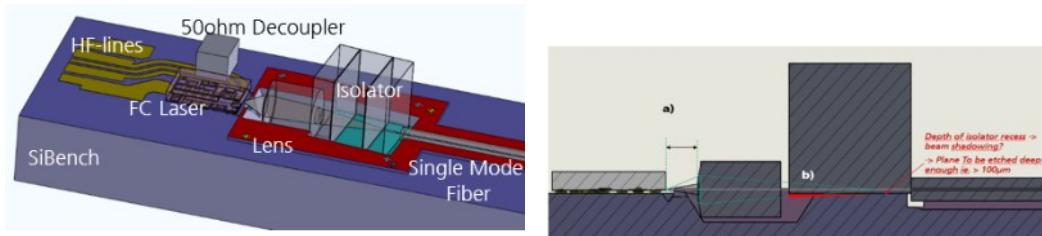

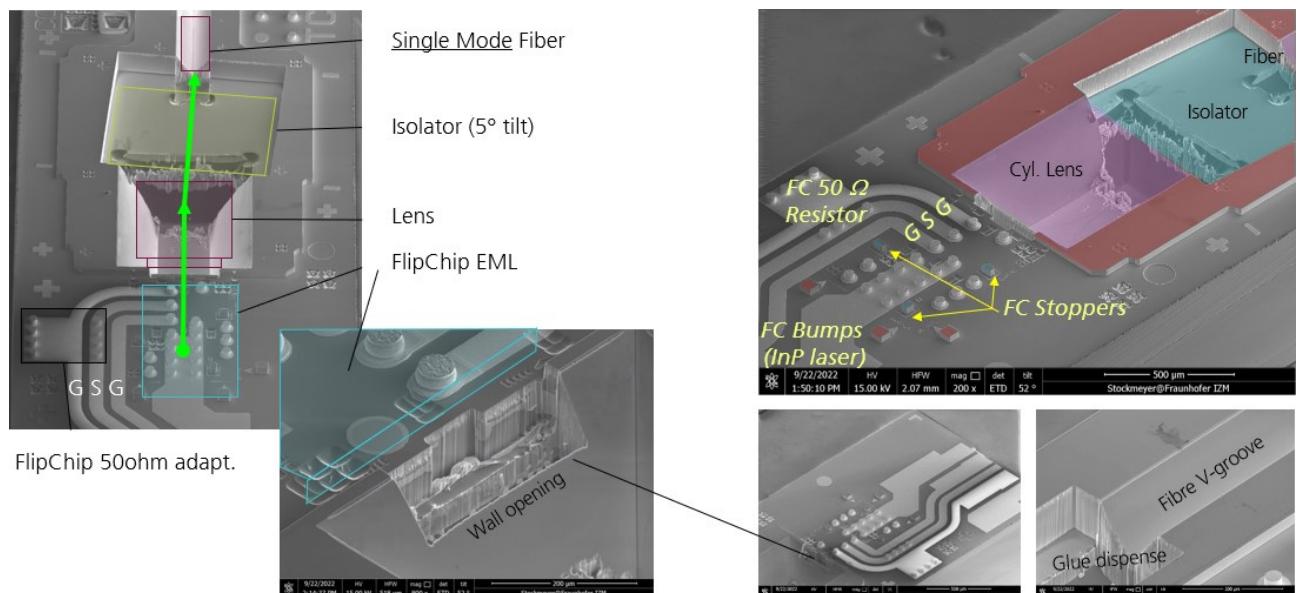

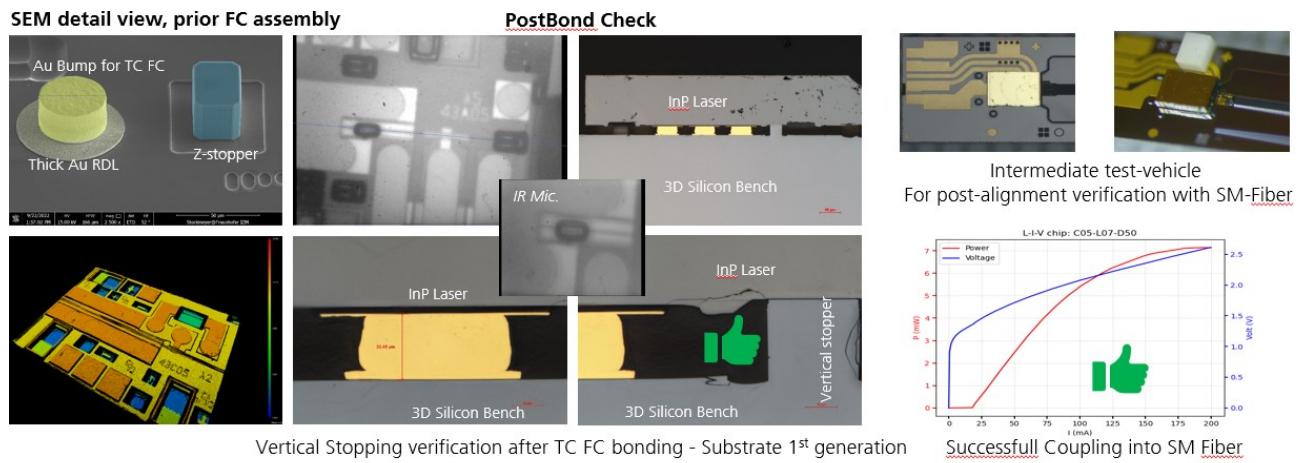

Im Fall der Applikation 3 ist die Fabrikation eines 3D-Silizium Bench inkl. Vielzahl an Sub-Varianten/Testvehicles mittels Silizium-Strukturierung abgeschlossen worden. Die Flip chip Verfahren sind für Integration der Laser Chips durchgeführt worden. Zusätzlich sind optische Bauelemente (Linse, Isolator) darauf montiert worden (nicht als vorgesehen Arbeitstask, Task BESI-AT). 3D Submounts (Silicon und Mold) sind auch an involvierten Partner (BESI Austria) für die präzise Assemblierung der optischen Teile (Die-Attach des Laser Die, Einbau Optik-Elementen) zur Verfügung gestellt worden.

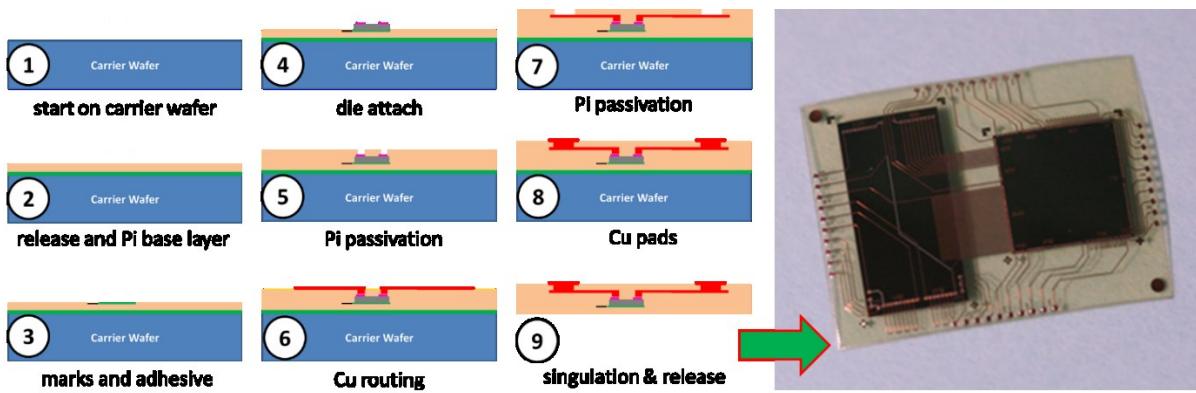

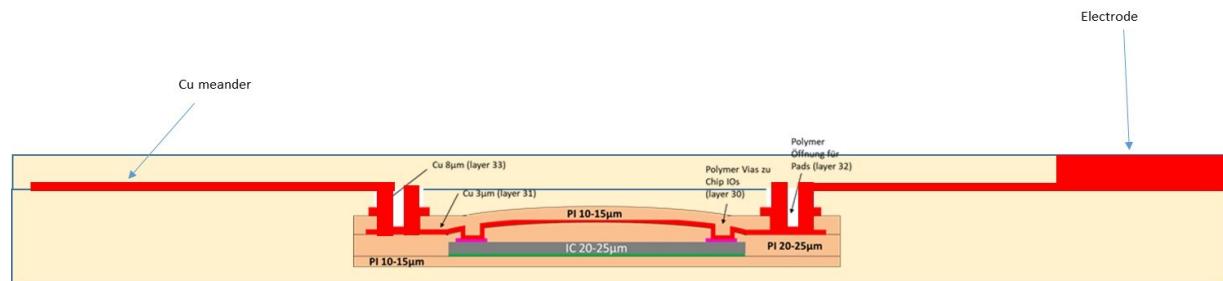

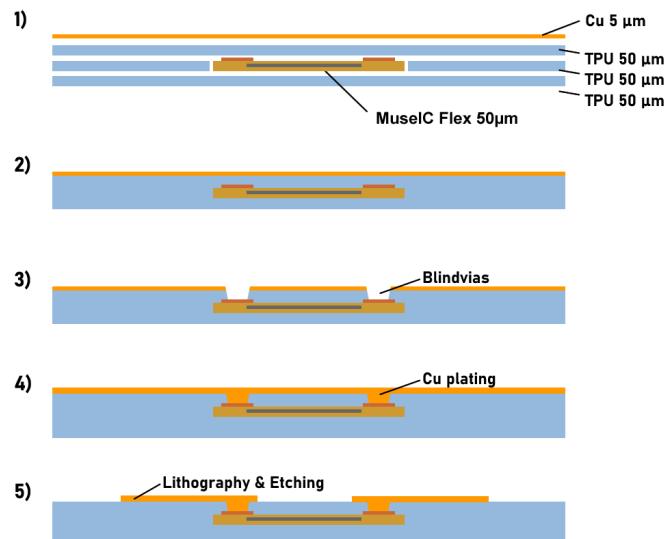

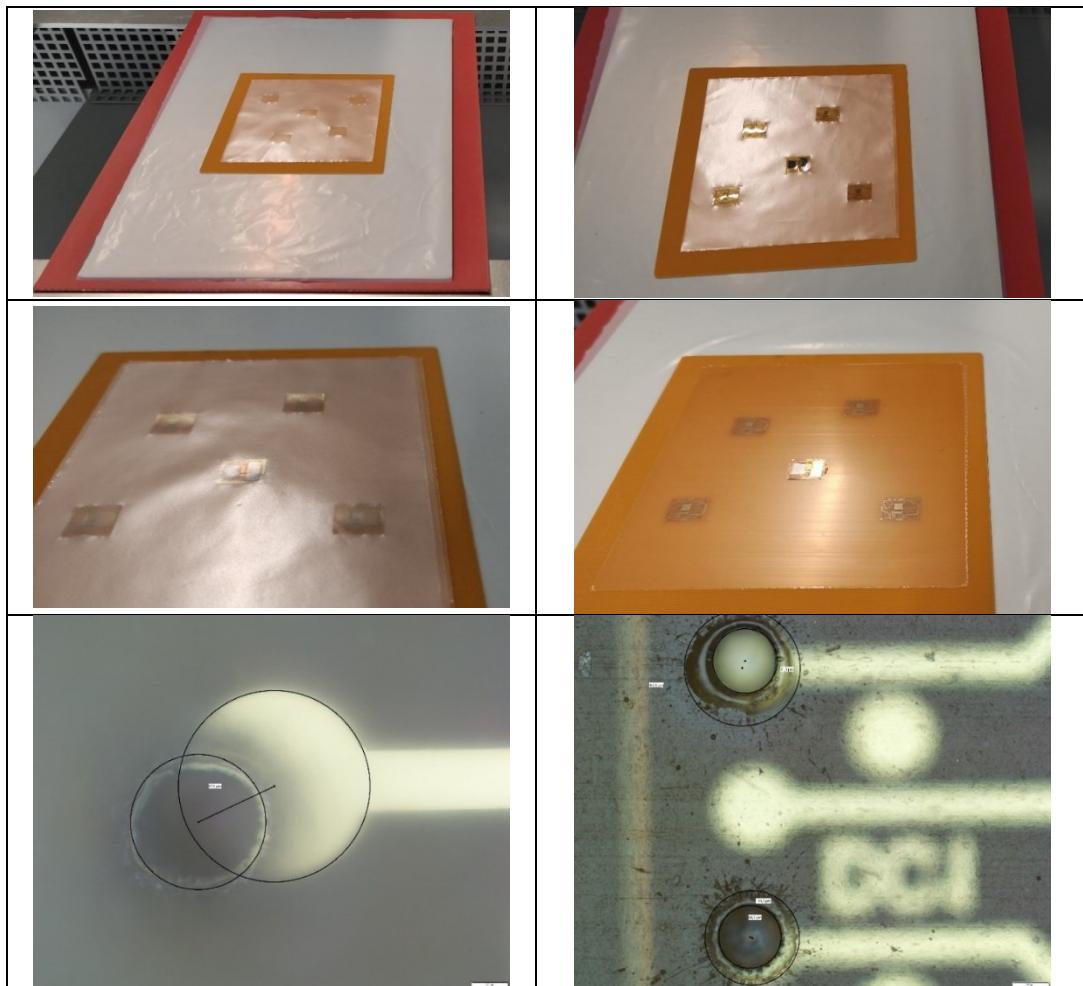

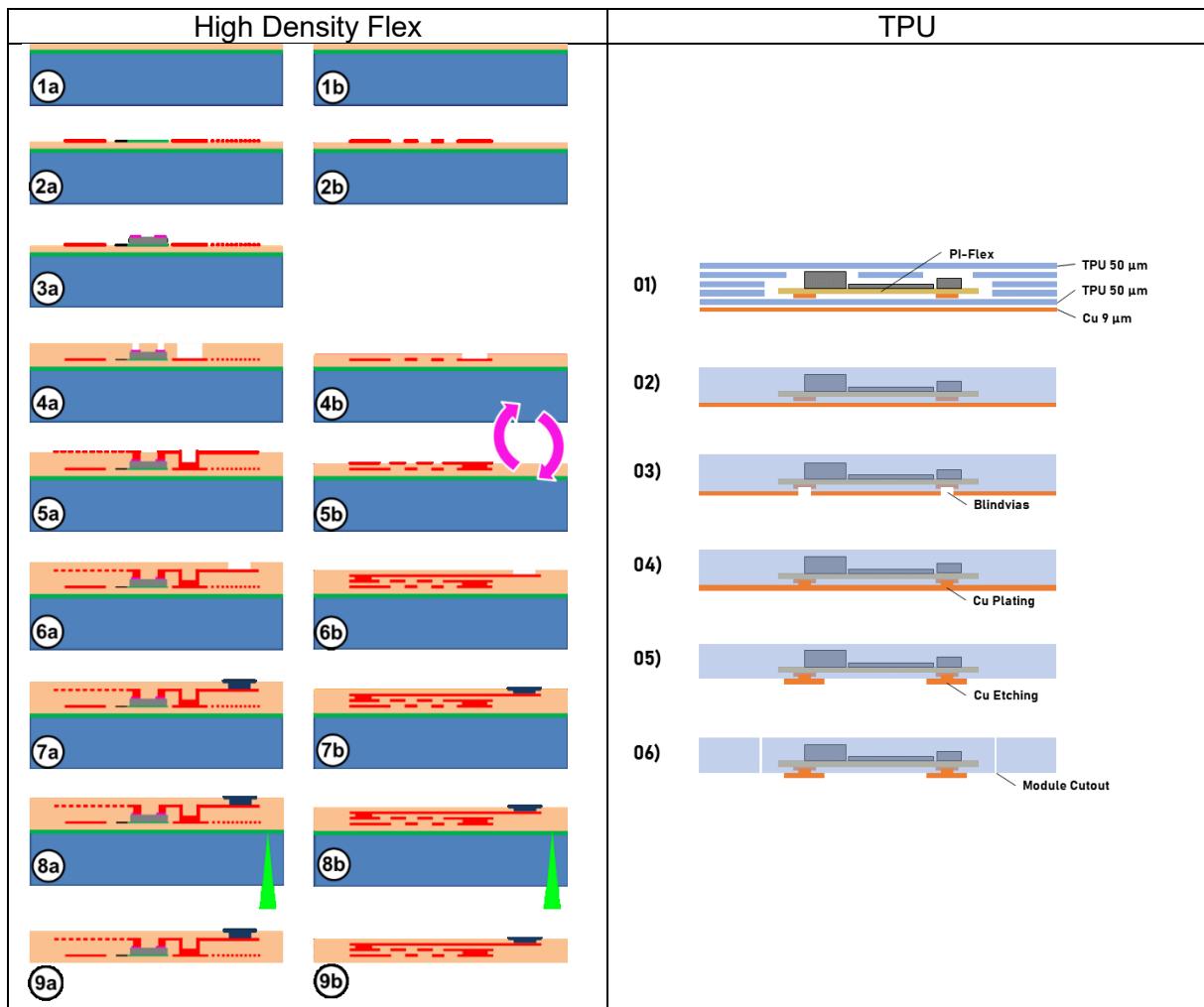

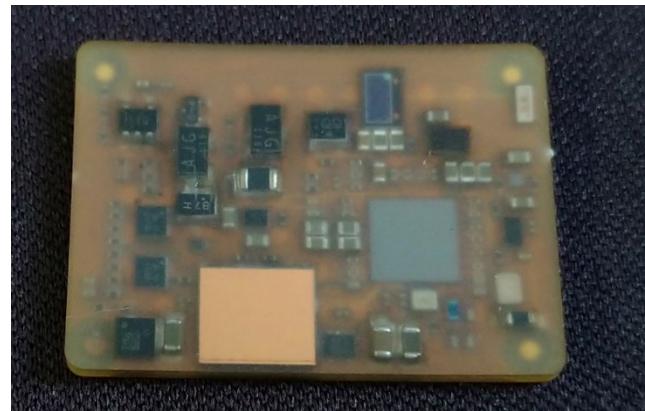

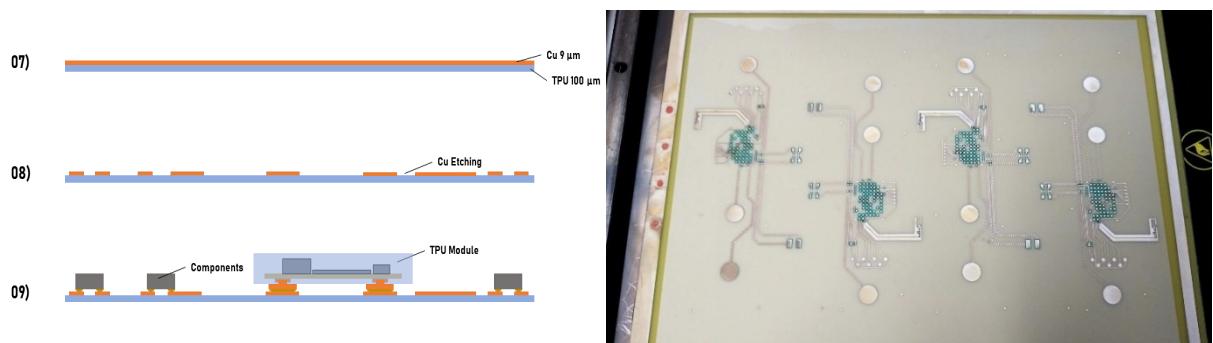

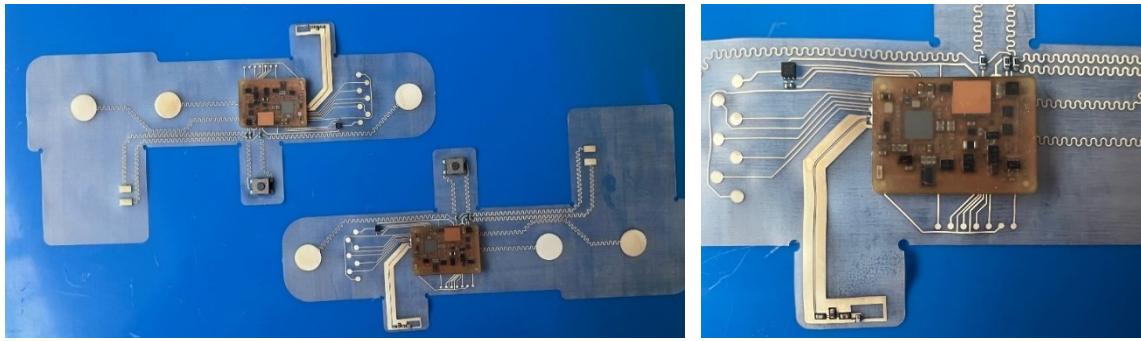

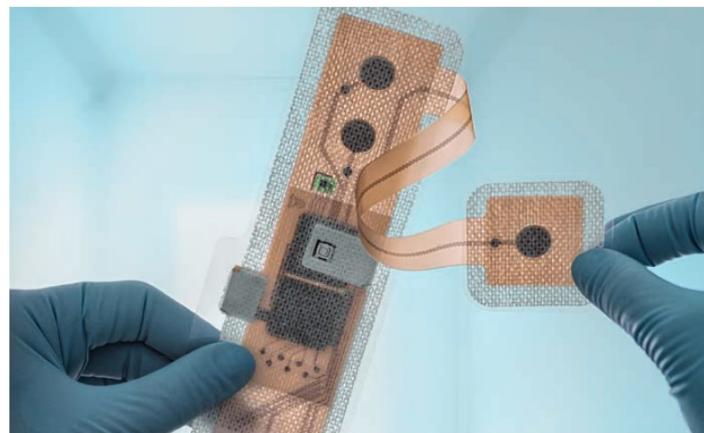

Im Rahmen der Applikation 4 ist der Flex-basierte Integration anhand funktionaler Teile erfolgreich durchgeführt worden. Hierbei sind High Density Polyimid basierte Flex Substrate hergestellt worden, worin bzw. worauf elektronische Bauelemente in unterschiedliche AVT (Flip chip und SMT) aufgebaut worden sind und in einem TPU flexible Material eingegossen. Nach korrekter Einbettung sind die Aussenkontakte finalisiert worden. Der Impakt vom Covid-19 und sanitären Gegenmaßnahmen ließen sich durch starkgebremsten Arbeit-fortschritte negativ spüren, insbesondere bei Prozessentwicklungen, wofür Home-Office nicht infrage kommen kann.

Der beiliegende Bericht fasst die unternommenen Arbeiten für die Gesamtzeitfenster des Projektes zusammen. Der folgende Sachbericht ist wie bei den Zwischenberichten auf Englisch weiterverfasst worden.

**2) Vergleich des Stands des Vorhabens mit der ursprünglichen (bzw. mit Zustimmung des ZG geänderten) Arbeits-, Zeit- und Kostenplanung.**

\* Das Vorhaben liegt im Wesentlichen innerhalb der ursprünglichen (bzw. mit Zustimmung des ZG geänderten) Arbeits-, Zeit- und Kostenplanung.

\* Eine Anpassung des Arbeitsplans wird erforderlich (Erläuterung erforderlich).

Nein

\* Es sind zeitliche Verzögerungen aufgetreten (Erläuterung erforderlich).

*Die sanitäre Lage hat erheblichen Weiterauswirkungen auf die Projekt-Arbeiten gehabt (beschränkten Personal-Anwesenheit, Krankmeldung vom Personal, Verspätungen in Wartungen und Services, etc). Aufgrund dessen ist das Projekt auf 42 Monate (M412 = Okt22) nach EU- sowie nationaler Bewilligungen kostenneutral verlängert worden.*

\* Es sind Mehr- oder Minderausgaben aufgetreten (Erläuterung erforderlich).

Nein

**3) Haben sich die Aussichten für das Erreichen der Ziele des Vorhabens innerhalb des angegebenen Berichtszeitraums gegenüber dem ursprünglichen Antrag geändert (Begründung)?**

\* Die Aussichten für das Erreichen der Ziele des Vorhabens haben sich gegenüber dem Zeitpunkt der Antragstellung nicht verändert.

\* Die Aussichten für das Erreichen der Ziele des Vorhabens haben sich geändert (Erläuterung erforderlich).

Die Aussichten haben sich im Jahr 2022 nicht geändert, dennoch:

Bei Applikation 2 ist die Bereitstellung von funktionalen Sensor Device Wafer durch Use Case Leader (MEMS Bolometer, IDEAS, Norwegen) letztendlich gescheitert. Sein externe Subcontractor war nicht in der Lage Sensoren zu finalisieren, die für das Projekt als Prozess- und Funktionsdemonstration vorgesehen waren. Die Arbeiten blieben unzufriedenstellend in dem Fall auf nicht-funktionalen / ShortLoop Mikrobolometer, ohne möglichen Nachweis auf Nieder-Vakuum Verkapselung (Niedervakuum notwendig für MEMS Funktion). Als Gegenmaßnahme wurde ein Pirani-Sensor von Fraunhofer IMS mittels Wafer Level Packaging am Fraunhofer IZM mit Silizium-Cap in Vakuum verkapselt, und hiermit das resultierende eingekapselte Vakuum in Zusammenarbeit mit USN / Norwegen (Pirani Design und Charakterisierung) evaluiert.

Die Applikation 3 litt der Rücktritt des Use Case Leaders (Dustphotonic, Israel) aus dem Konsortium. Der passive Aufbau der Optik-Teilen (Linse, Isolator, Faser) auf dem Silizium Bench für vollständige Assemblierung eines Transmitter-Submodule sollte vom Partner BESI-AT übernommen werden (komplette Assembly sollte für das 3D Mold Substrate gemäß Projekt ohnehin dort erfolgen), blieb aber bei Projekt-Abschluss ausstehend. Die in 2023 von BESI-

AT vervollständigt-aufgebauten Submounts erwiesen sich lediglich als nicht genug präzis-assembliert.

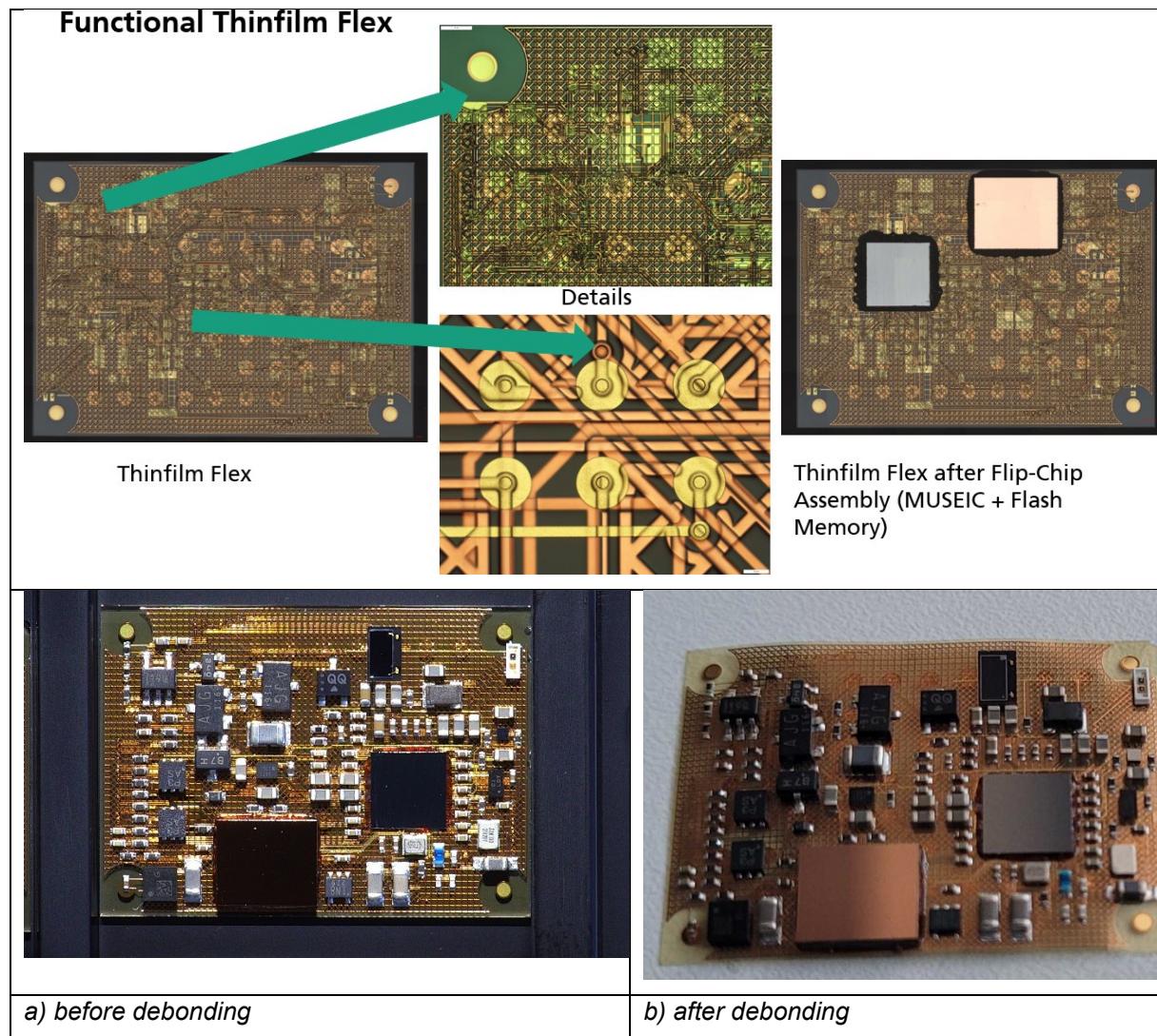

Bei der Applikation 4 sind die funktionalen Chips (IC, Flash Memory) nicht im Flex-Substrate eingebettet, sondern auf Flex-Substrate geflippt und anschliessend ist der Flip chip Flex in flexibles Material für die Patch-Herstellung eingebettet worden. Hintergrund war einerseits der hohe Risk bei rückdünnen von hoch integrierten Prozessor MUSEIC chips von IMEC-NL kombiniert an kanppe und verzögerte Verfügbarkeit von funktionalen einzel-chips, um dies vorzutesten. Anderseits die Flash Memory Chips hätten höchstwahrscheinlich das thermische Budget des Gesamtprozesses nicht überstanden.

**4) Sind inzwischen von dritter Seite FuE-Ergebnisse bekannt geworden, die für die Durchführung des Vorhabens relevant sind?**

- \* Nein

\* Ja (Erläuterung erforderlich)

**5) Sind oder werden Änderungen in der Zielsetzung notwendig?**

- \* Nein

\* Ja (Erläuterung erforderlich)

**6) Jährliche Fortschreibung des Verwertungsplans. Diese soll, soweit im Einzelfall zutreffend, Angaben zu folgenden Punkten enthalten:**

- \* Im Berichtszeitraum wurden auf Basis der Ergebnisse des Vorhabens Schutzrechte angemeldet, erteilt oder eine Anmeldung vorbereitet (Erläuterung erforderlich).

Nein.

- \* Im Berichtszeitraum sind Änderungen der wirtschaftlichen Erfolgsaussichten nach Projektende gegenüber der Darstellung im Antrag aufgetreten (Erläuterung erforderlich).

Nein.

- \* Im Berichtszeitraum sind Änderungen der wissenschaftlichen und/oder technischen Erfolgsaussichten nach Projektende gegenüber der Darstellung im Antrag aufgetreten (Erläuterung erforderlich).

Nein.

- \* Im Berichtszeitraum sind Änderungen der wissenschaftlichen und wirtschaftlichen Anschlussfähigkeit gegenüber der Darstellung im Antrag aufgetreten (Erläuterung erforderlich).

Nein.

## Part II: Technical report

### WP1 Management

#### Task 1.1 Technical Coordination

Fraunhofer IZM leaded work package 5 and coordinated the cooperation between the partners within this work package. Fraunhofer IZM supported the overall project coordination by ICOS (BE) and Spinverse (FI) regarding the implementation of the application scenarios and technical support.

Work related to project management was concentrated on participation to monthly TCC online meetings (Technical coordination committee) and following developments in other Work Packages especially WP3 and WP4, since most of works had to be transferred into WP5 based on progresses and lessons learned in WP4. For the UCs wherein Fraunhofer IZM was directly involved, collaboration dealled directly inside the UC clusters and with respective UC owners.

### WP2 Requirements and Specifications

#### Task 2.2 Requirements and specifications for UC2 (Low cost thermal imaging systems)

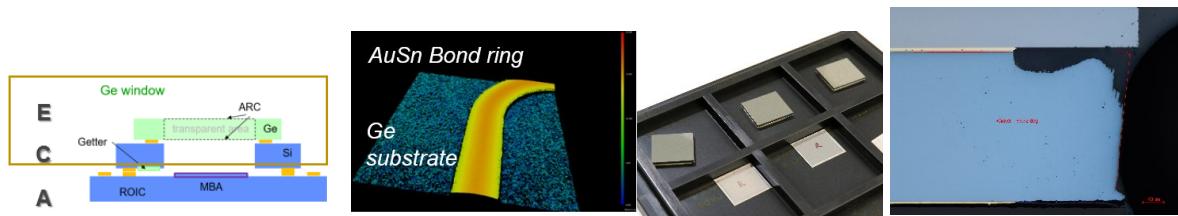

In UC2, Fraunhofer IZM was contributor for wafer level packaging of a low-cost thermal image system, owned by the UC owner/leader IDEAS (Norway). For vacuum packaging of IR camera, a lid was developed with a transparent window and bonded to a bolometer chip at wafer level and hermetically sealed.

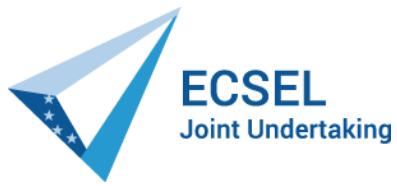

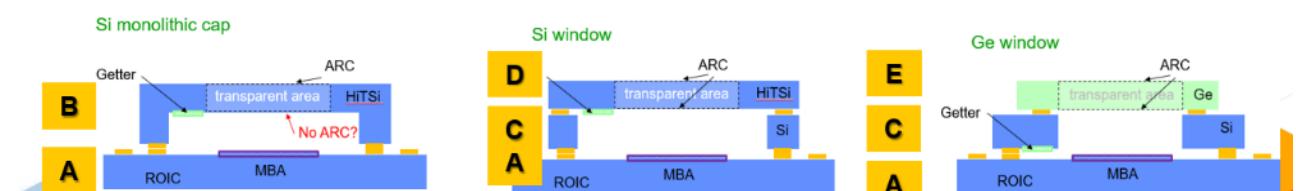

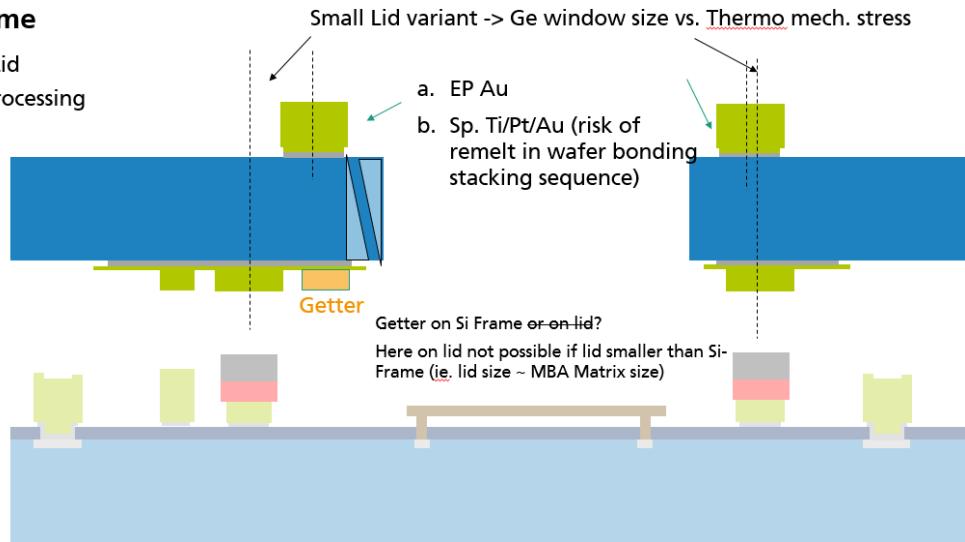

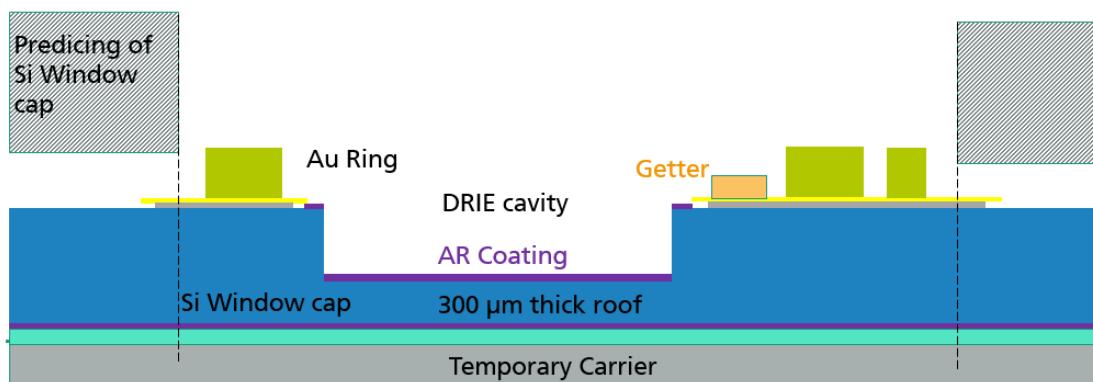

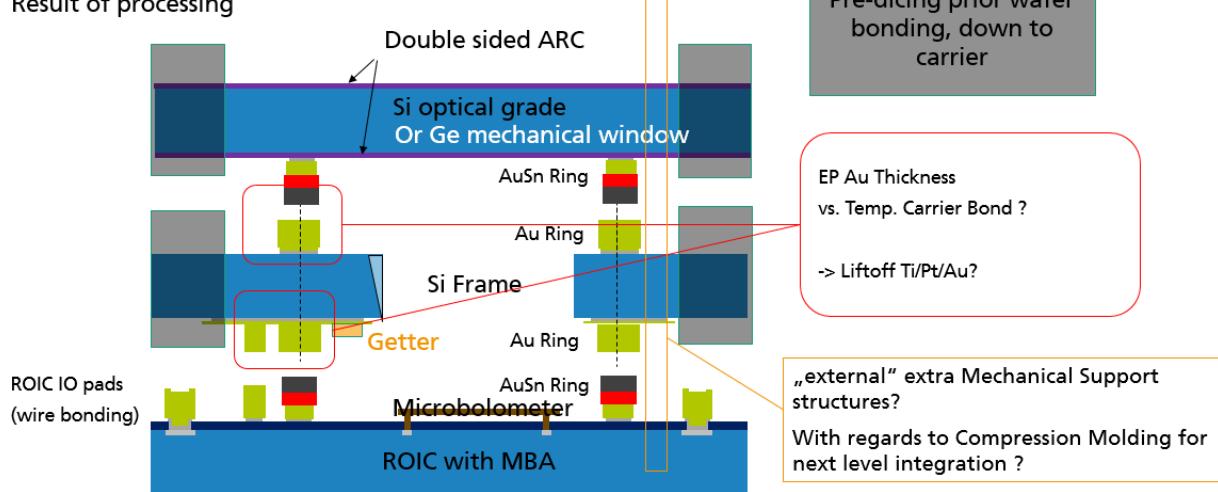

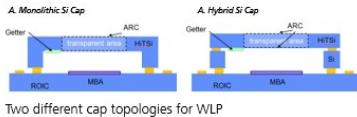

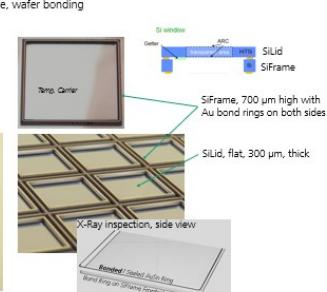

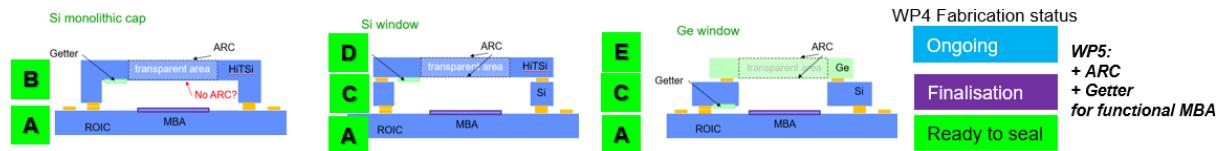

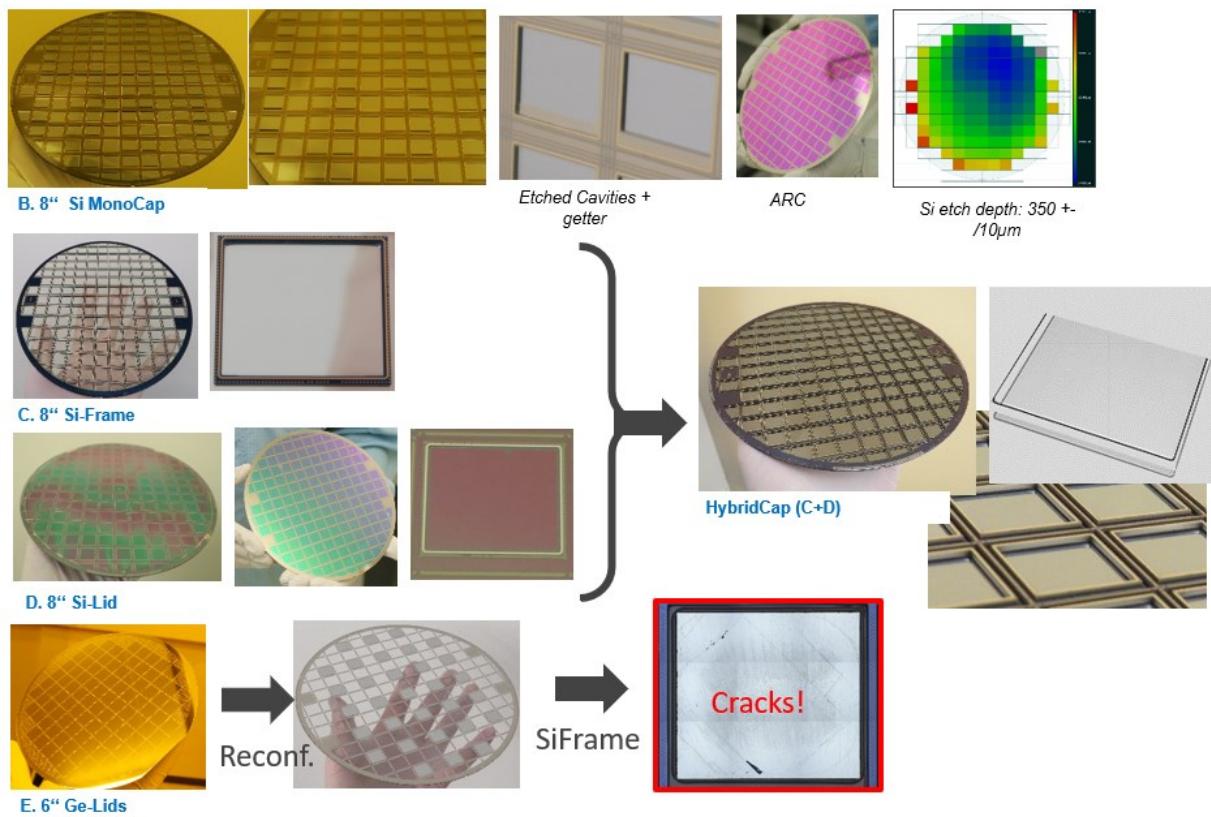

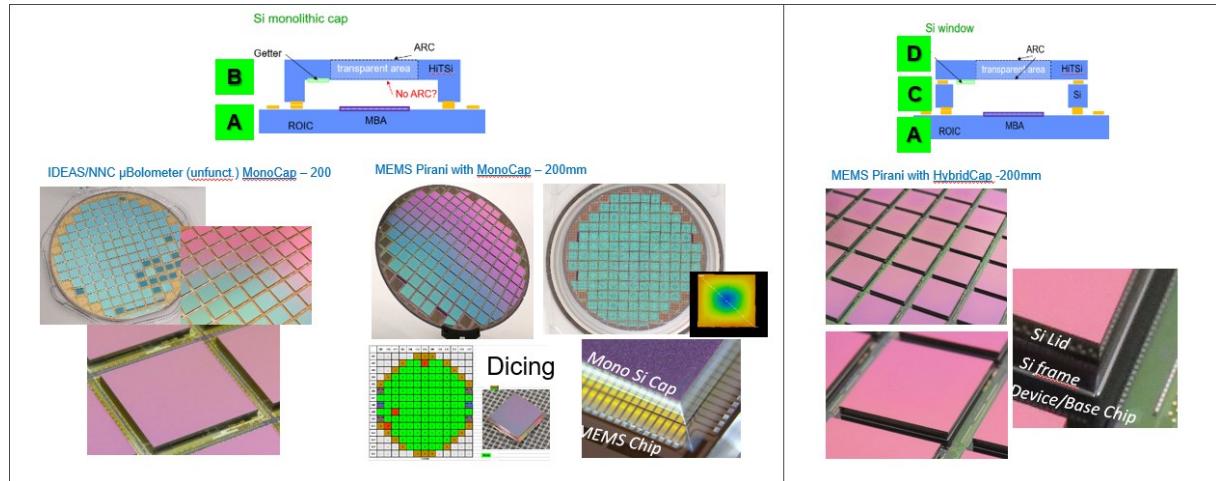

Different capping structures (Figure 1) and window materials were first compared and validated against the objectives. Due to cost constraints and lifetime expectations a highly transparent silicon (HiTSi) window has been retained instead of Germanium as originally planned.

For longer lifetime the variant based on silicon (Si) frame should provide a large vacuum capacity and allows the deposition of getter material. Depending on the cap topology, the achievable internal volume differs largely as well as internal volume-to-surface ratio, which might have some influences on the functionality of the MBA. Also, double (upper sketches, "Ge-Window" and "Si window") or single (lower sketches, "Si monolithic" and "Si flat lid") seal bonding were considered depending on the topology, these being reflected in the complexity of the corresponding process flow.

At Task.2.2 level, it was foreseen to compare a Ge-based and a Si-based window topology regarding the sealing feasibility and reliability. Some questions were clarified, regarding the bolometer provided by IDEAS in the way of delivery form, i.e. In other terms how the bolometer wafer technically looks like, especially regarding protection of the bolometer structures vs. Processing compatibility.

For cap fabrication, different suppliers were contacted, with focus on European collaboration, for silicon and AR coating. Two possible suppliers for the Si Wafer for providing the lid were identified, the first one in Germany (with also the possibility of deposition of the required Anti-Reflective Coating), and the other one in Denmark (only the base material, drawback: ARC should be applied by another external supplier).

The feasibility of incorporating an AR coating inside the structured Si monolithic cap was also considered (AR coating being not in the consortium capabilities and will be subcontracted to third one). However, the inner AR coating was not implemented and withdrawn, to limit complexity and save process time as debated with UC2 Owner IDEAS.

An industrial German AR supplier for deposition on 200mm wafer could be also identified for the wavelength range, i.e. for Si substrate in the LWIR range, and for 200 mm wafers, the main constraint regarding WLP at FhG-IZM. The coating was tested on monitor wafers regarding compliancy with process flow (WP4, 5 and WP6).

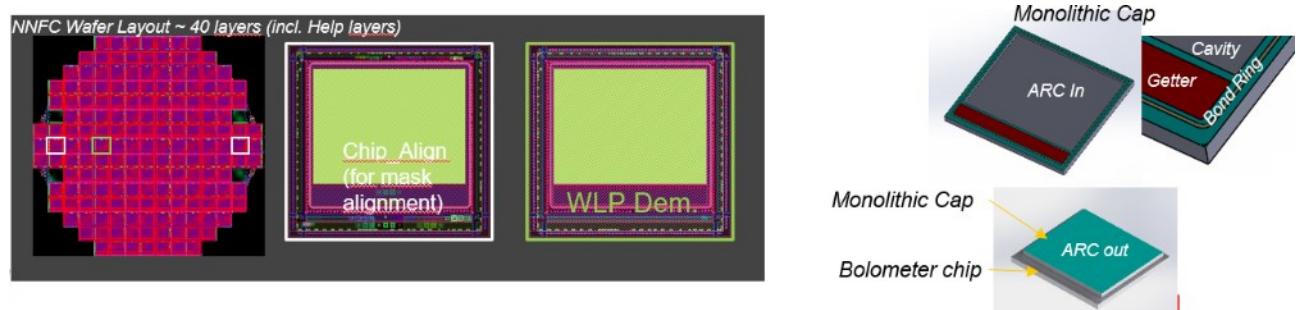

Figure 1: Cap topologies considered for the WLP of the microbolometer, based on Germanium or/and Silicon window material

On the side of wafer level packaging, the main requirements as defined/revised can be globally summarized as follow:

- Cap thickness:

A 300  $\mu\text{m}$  silicon thickness has been chosen for roof thickness of the monolithic silicon cap and Silicon Lids, since providing mechanical robustness (in view of advanced packaging, especially Die Attach and Molding at consortium partner sides) and a minor bending of few micrometers (based on mechanical estimation of pressure difference), which should be measurable but also without any impact on optical aspects (transmission and distortion).

- Silicon Body thickness:

Total thickness of monolithic silicon cap will be in the range of 650  $\mu\text{m}$  as from provider, and the silicon frame in the range of 700  $\mu\text{m}$ .

- Cap size:

The cap size and sealing ring location should permit a 500  $\mu\text{m}$  clearance to the pad ring with the wire bond contacts.

- Bond rings:

1 Gold-based (gold on one side and gold-tin on the other side) sealing bond ring of ca. 10  $\mu\text{m}$  total thickness have been selected to enable AuSn soldering. The gold-tin ring will be applied on bolometer side and silicon lids, the monolithic cap and frame with gold rings.

- 2 Since the IDEAS Bolometer might only be provided with a very thin top oxide of 20 nm, the seal ring should not lay over critical areas where last metal is only covered by this top oxide. Discussed and fixed in coordination with IDEAS.

- Anti-reflective coating:

Anti-reflective coating for LWIR spectrum is only applied on the outer side of the capping parts, as discussed with end user / use case leader. The coating will be protected during wafer level processing, to avoid any damages / scratches during handling and process phases.

- Getter:

A getter will be applied inside the package and provided by subcontractor. Interface to subcontractor (wafer alignment, clearances, size maximized accordingly) has been here clarified.

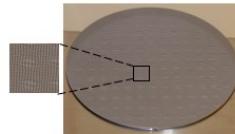

The device/Bolometer wafers were provided with Semi-Notch (Fraunhofer IMS) and Flat (IDEAS with its subcontractor NNFC/South Korea). In this case a flat-to-notch adapter has been required to allow processing on the needed stations of the technological park of Fraunhofer IZM.

In view of hermetic packaging, special countermeasures were implemented in the process flow at Fraunhofer IZM.

The requirements were synthesized with UC contributors in the EU Deliverable D2.2: Requirements and specifications for UC2: Low cost thermal imaging system.

### Task 2.3 Requirements and specifications for UC3 (Passive fibre alignment for single-mode transceivers)

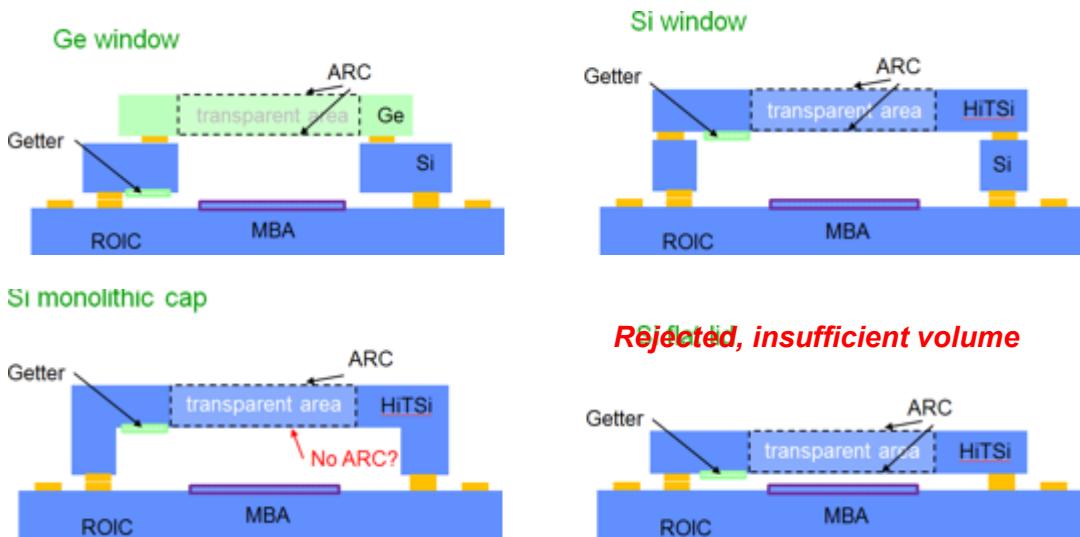

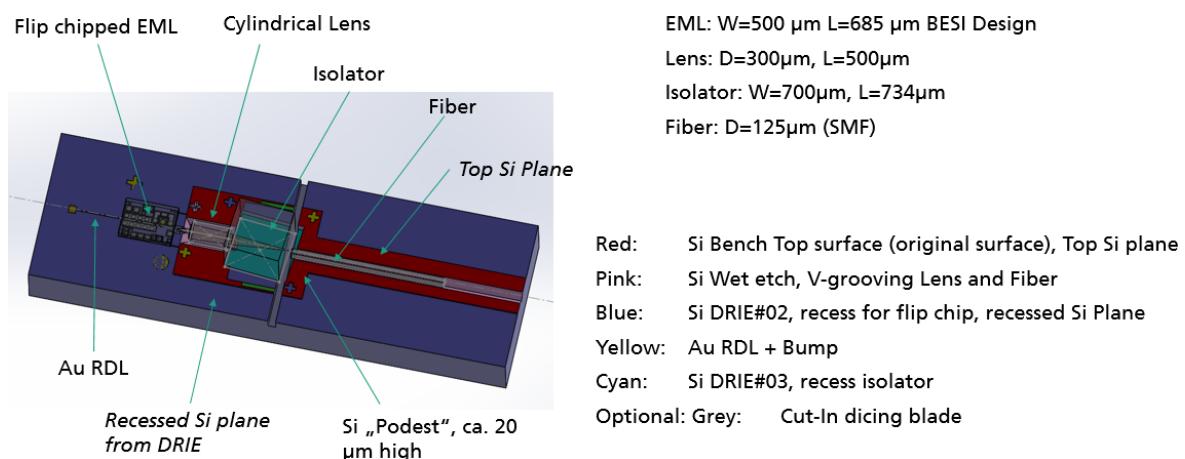

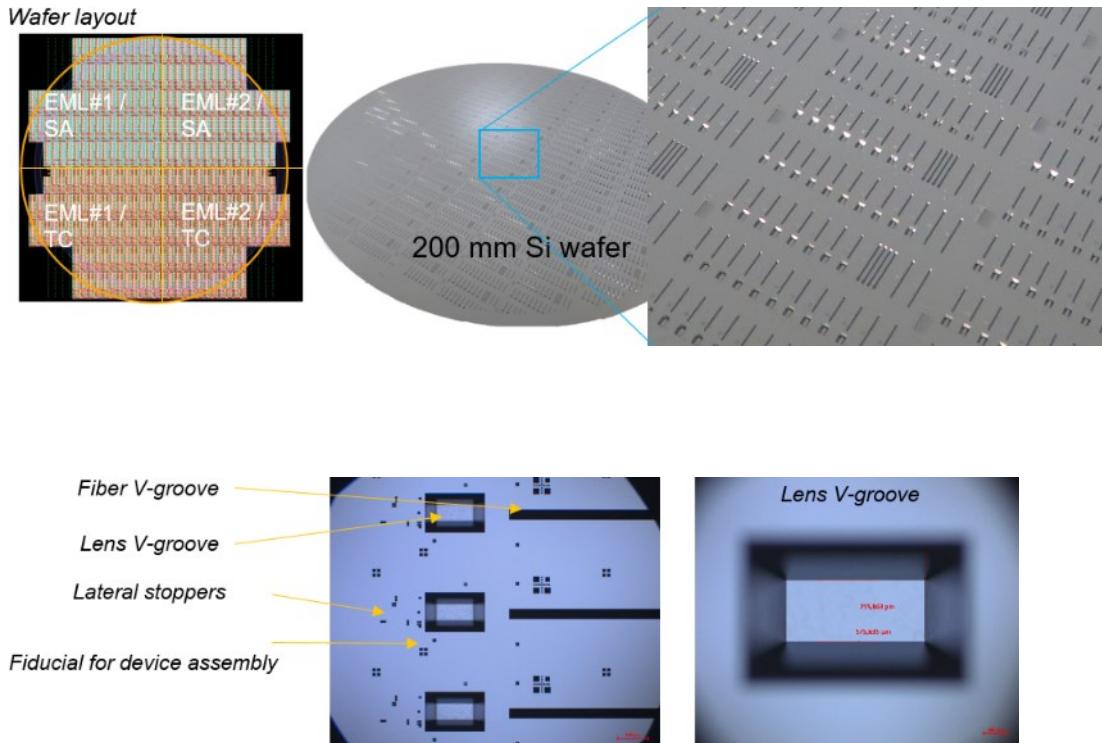

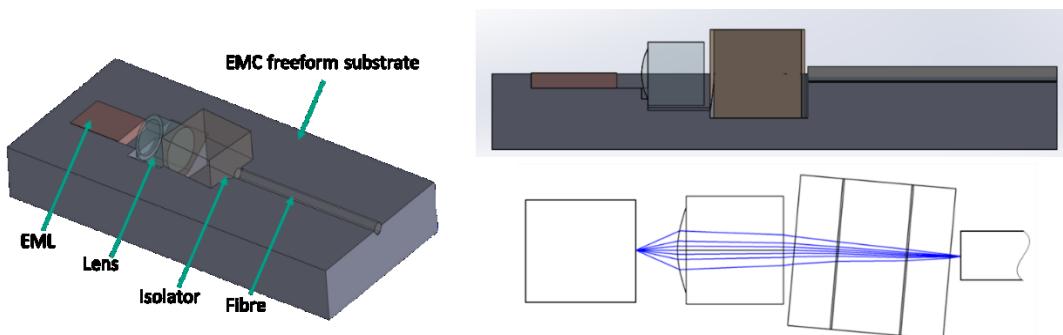

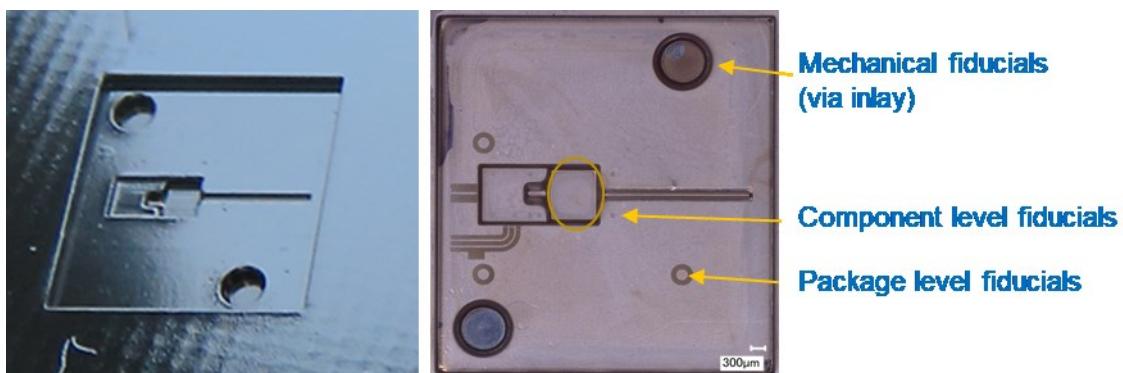

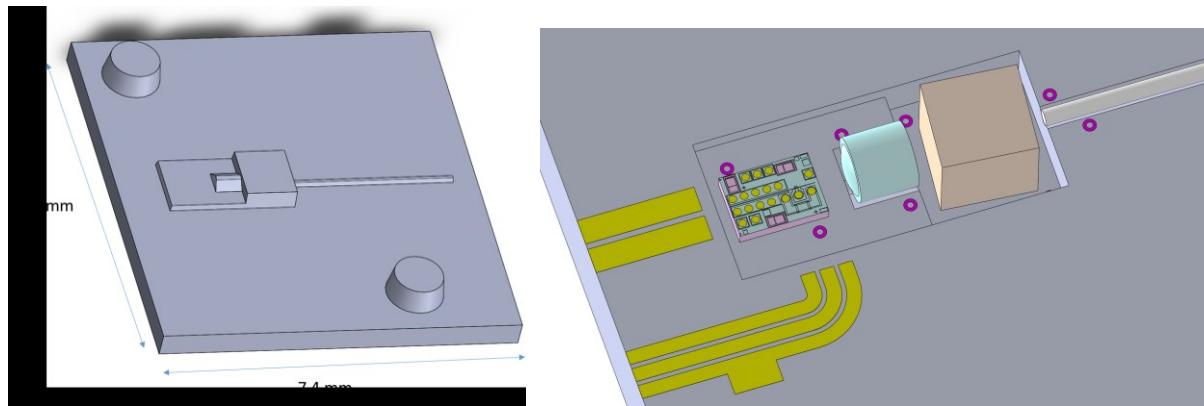

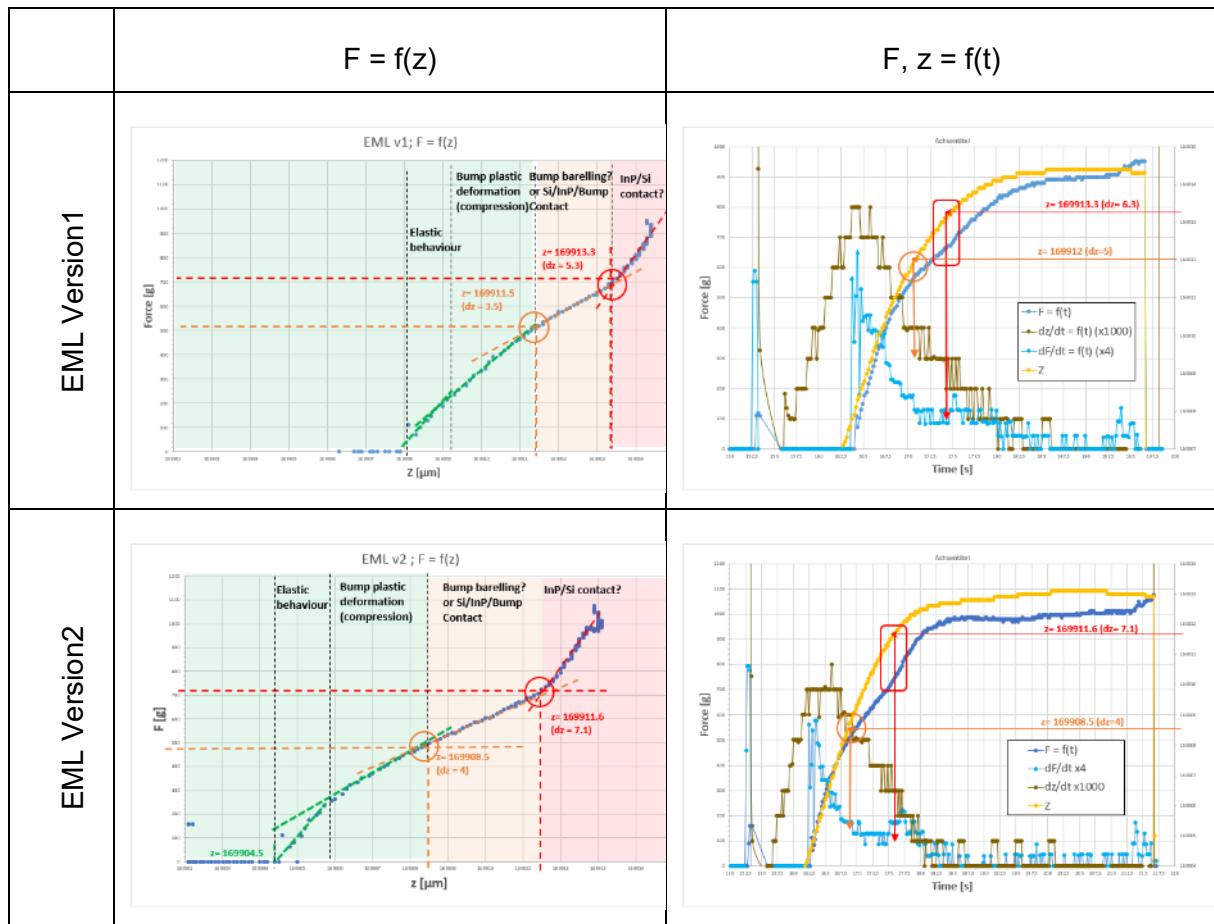

The use case 3 pursues the goal of fabricating a single mode transceiver. Within the use case, intention was to develop a process for high precision bonding of EML components onto an optical bench to allow for passive fibre alignment relative to the EML/laser source. The silicon bench comprises 4 channels à 1.6mm Pitch, which should fit within the transceiver board (Figure 2).

Figure 2. 3D-view of the transceiver of DPH with the 4Channel submount (in red square), Schematic of the for the passive alignment of the EML; basic sketch of the Si-bench with self-aligned EML and optical components (right)

The requirements are especially focused on the side of Fraunhofer IZM on the passive alignment and all the required geometries. The silicon bench was first drafted using CAD software to better apprehend the needed 3D geometry (Figure 3).

The results of the optical simulation performed by DustPhotonics with the arrangement of the single optical elements “cylindrical lens + Isolator + Fiber” were included in the 3D model, in order to derive the entire required geometry of the silicon bench and all the needed relative spaces and depths.

Figure 3: 3D-CAD layout of the Unit Cell (1x Channel) of the silicon optical bench with EML device flipped and metallically bonded to Si bench, cylindrical lens, isolator and Fiber with recesses/v-grooves and fiducials (HF routing on silicon not represented)

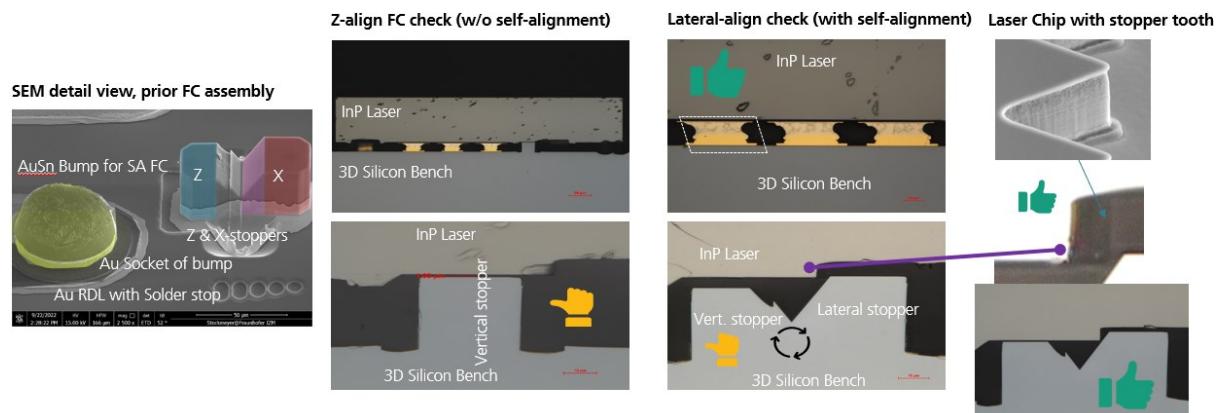

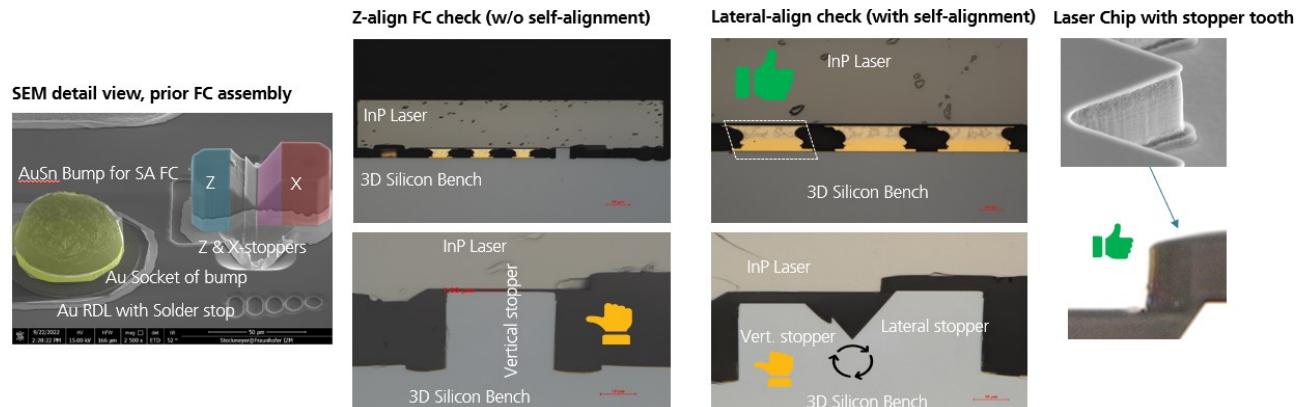

On the side of precise flip chip assembly, two different approaches to achieve precise passive bonding of the laser in flip chip were at this level/task considered:

1. Liquid solder assisted self-alignment of EML devices to the silicon bench with mechanical stops. Lateral stoppers and v-groove must be fabricated in a same mask so that they are defined in a same lithography process, bypassing any mask-to-mask (or design layer to design layer) shift caused by mask registration/alignment.

2. High precision thermocompression bonding with electroplated gold bumps onto the silicon bench. The Assembly is to be performed using a flip chip bonder presently available at FhG-IZM. The bonder has been purchased some months ago and according to the manufacturer allows assembly with a bonding precision down to 0.5  $\mu\text{m}$ .

Two different variants of the EML device were foreseen and conceived/co-designed with the laser fabricant of the consortium ALMAE (France):

- straight, i.e. the laser beam output is perpendicular to the facet,

- 7° tilted, the laser source is tilted from the facet by a 7° angle to avoid back reflection into the chip, as explorative work.

Where both are intended to be used for solder self-alignment as well as for thermocompression bonding. This boundary rises the number of base layouts to the quantity of 4 (2x different flip chip technologies, 2x chip variants), to be conceived and included in the Wafer layout.

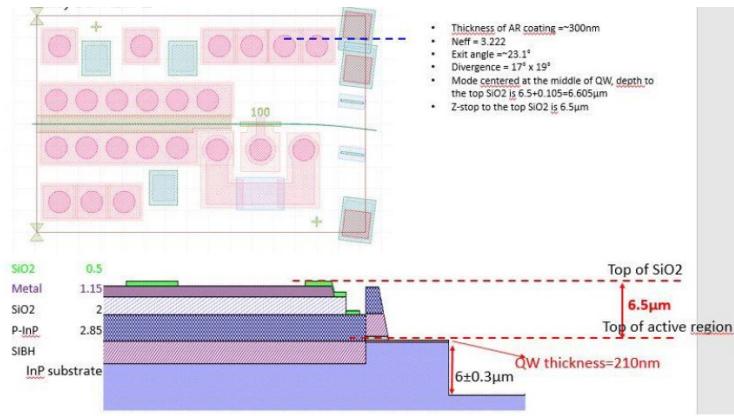

Figure 4. Depth definition of the recesses in the InP EML devices by ALMAE

FhG IZM has also jointly worked with ALMAE, France (InP laser provider) and Dustphotonics (first Use Case Leader, Israel) on design features so to implement the needed mechanical stoppers into the EML (definition of the etching depths in InP, sizing of recesses for z-Spacer and X/Y stoppers, fiducials in MQW optical layer) and the silicon bench. A sketch in cross-section from ALMAE recapitulates the technical feasible layer stack of the InP (Figure 4).

A keep out distance of the pads to the facet was also considered in chip version 2. Effectively it was found that the Antireflection Coating is being applied over the pads by the deposition process and the pads are not far enough from facet, affecting the solderability of the pads for self-alignment. The IOs of the InP FC component were terminated with TiPtAu (Au ~ 1µm).

The 2 chip versions further increased by 8 the number of base layouts needed (2x different flip chip technologies, 2x chip variants (straight and tilt), 2 chip versions/generations)

### Recesses for X/Y stoppers and Z-stoppers

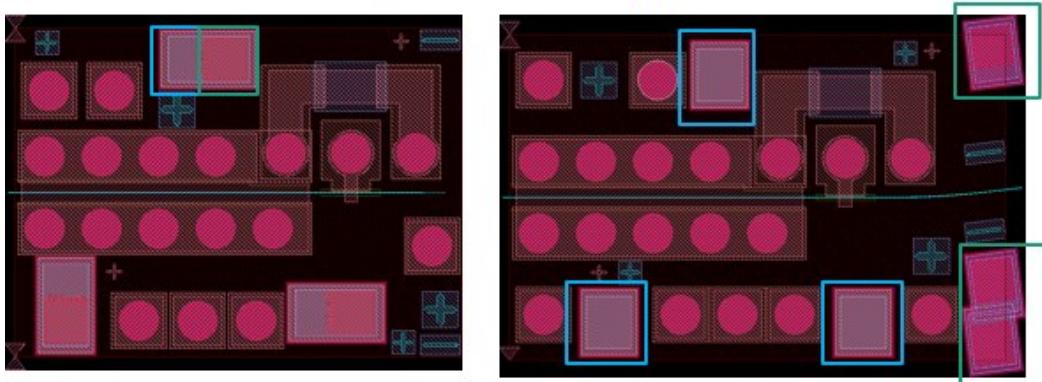

Figure 5: Overview of both GDS Layouts of ALMAE's EML devices (straight EML, left, and Tilt EML, right), devices size 500x685 µm und 500x780µm

The relative optical arrangement of the different elements (Figure 5) were fixed at M10, and implemented in the design (WP3) of the silicon bench. Several extensive iterations for layouting of the silicon bench were necessary, taking into consideration the foreseen sizes of the needed single elements / free space optics (lens + isolator) and the glass SM fibers as of D2.3 (see Table 1).

The EU deliverable D2.3 (“Requirements and specifications for UC3: Passive fibre alignment for single mode transceivers”) summarized the relevant Use Case requirements.

| <u>Lens:</u>                                                                                                                                                                                                                                                                                                          | <u>Isolator</u>                                                                                                                                                                                                 | <u>Fiber:</u>                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"> <li>• Diameter: 500 <math>\mu\text{m}</math> outer diameter, nominal</li> <li>• V-groove width: 617.9 <math>\mu\text{m}</math> (without compensation of silicon oxide thickness for Bench passivation)</li> <li>• V-Groove depth: at least 250 <math>\mu\text{m}</math></li> </ul> | <ul style="list-style-type: none"> <li>• Footprint Size: 700x734 <math>\mu\text{m}</math></li> <li>• Groove depth at least &gt;73<math>\mu\text{m}</math> (vertical beam diameter at this interface)</li> </ul> | <ul style="list-style-type: none"> <li>• Diameter: 125 <math>\mu\text{m}</math> outer diameter, nominal</li> <li>• V-Groove Width: 158.6 <math>\mu\text{m}</math> (without compensation of silicon oxide thickness for Bench passivation)</li> </ul> |

Table 1: Free optic elements for UC3 from DustPhotonics

## Task 2.4 Requirements and specifications for UC4 (Cardiac monitoring patch)

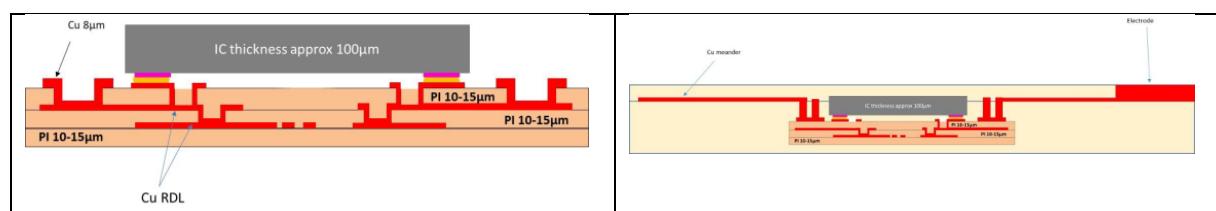

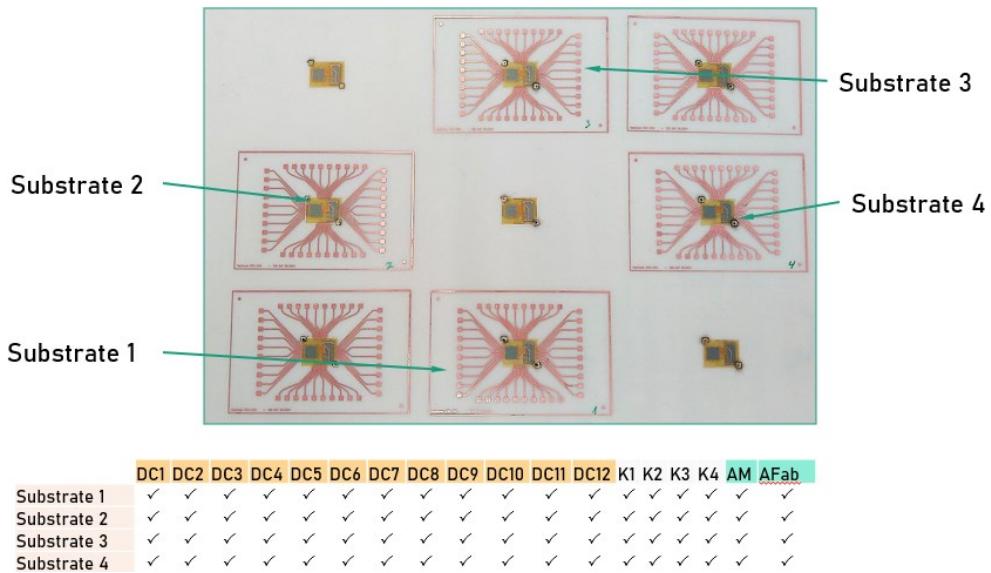

Fraunhofer IZM has provided specifications within the consortium for the design of the high-density flex with the embedded ICs as well as the stretchable substrate. The specifications included amongst others the required and expected thickness for dies to be embedded and the material stack layup for the flex and stretchable circuits. Furthermore, possible lateral dimensions of routing lines, vias and electrical and mechanical properties of the materials were fixed.

The layout rules were agreed with the project partners such as WE (Würth Elektronik) to enable a later process transfer. Additionally, expected placement accuracies and associated required IO pad, capture pad and interconnect dimensions were defined so that a proper connectivity between the several components of the flex/stretchable subsystem can be securely ensured.

First, a test vehicle was designed, using only dummy chips, for the purpose of fabrication feasibility and testing of single processes and reliability. After that, a second prototype was designed from the lessons-learned of this test vehicle, to process functional devices towards a functional flexible prototype.

For the functional prototype, a major change was implemented within the project: the processor chip being finally only available in form of few devices in multi-project wafer (wafer level thinning of devices not possible and high residual stresses in single devices), and the RAM memory chip not withstanding high temperature (required a.o. for polymer curing in thin flex embedding) it was decided to mount the active devices on the top surface of high-density flex instead embedding them inside it.

The requirements were synthesized with UC contributors in the EU Deliverable D2.4: Requirements and specifications for UC4: Cardiac Monitoring Patch.

## WP3 Design, Modelling & Simulation

### Task 3.2 UC2 design (Low cost thermal imaging systems)

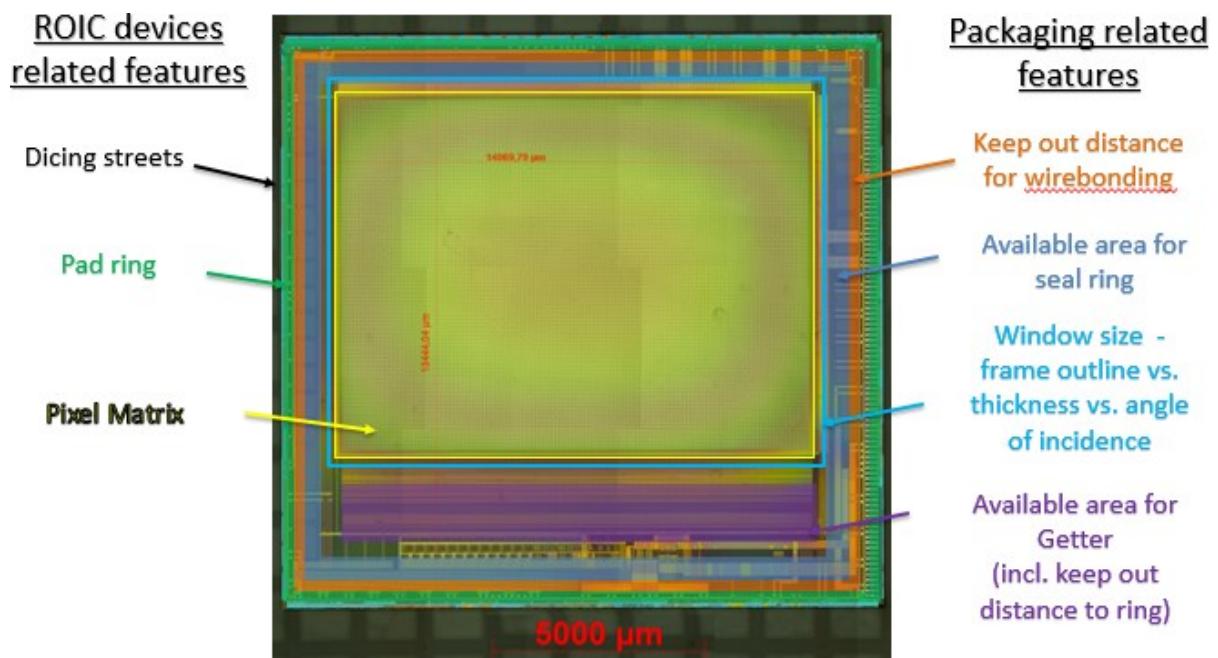

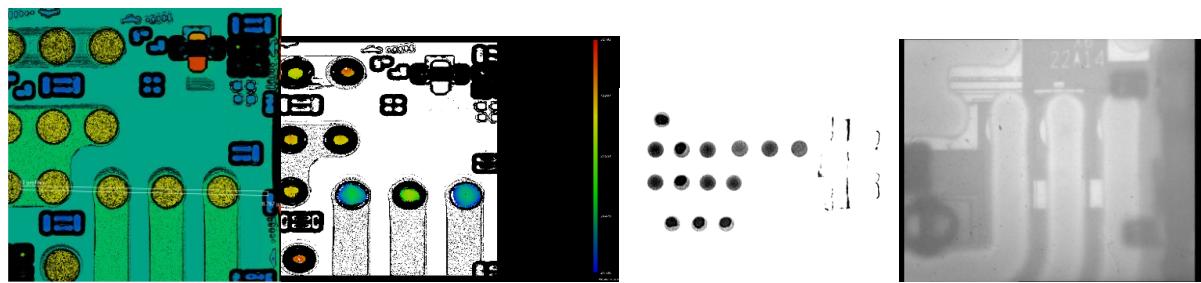

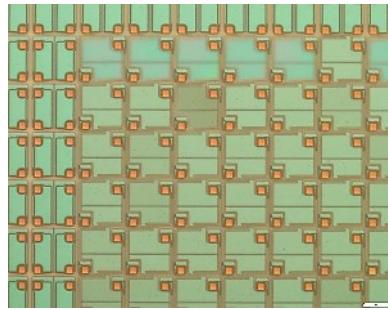

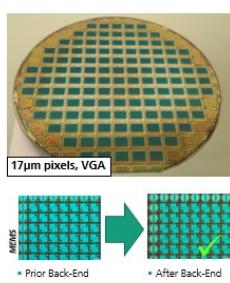

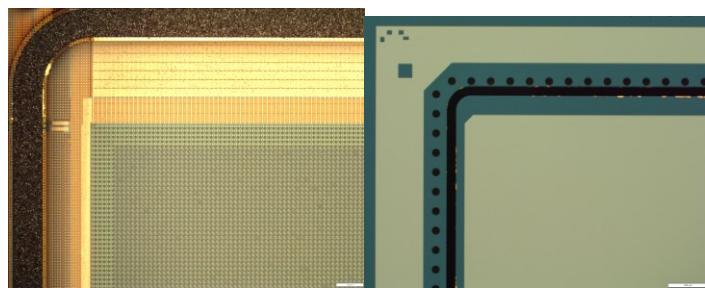

Work has been mainly focused on the design definition jointly with structuring process flows to be performed at FhG IZM (Figure 6). GDSII file of the ROIC chip (CMOS read out IC) and 17 $\mu$ m pitch MBA (Microbolometer Array, thin MEMS membrane, forming the pixels of the imaging systems) has been finalized and has been provided by IDEAS (chip layout with wafer shoot map) in Januar 2020 for first design drafts and alignments.

Figure 6: Example of IDEAS ROIC chip with packaging related features

Design of the ROIC/bolometer 200mm wafer layout has been reconstructed based on the ASIC shot map of the ROIC/bolometer chip and the single chip GDS (last metal layer and top passivation opening). Wafer layout were controlled and verified by comparing to a probe card wafer delivered in Mai20, which permit to fix the wafer layout grid and to circumvent any possible physical mismatch by 9' mask designing for WLP.

WLP features have been implemented based on D2.2 boundaries, for example for the sealing bond rings depending on ROIC/bolometer top passivation thickness vs. bondring line crossing of top metal layer of ROIC as well as correspondingly to the considered cap topology/ies.

The wafer layout was iteratively improved and finalized, regarding design for Wafer Level Packaging (co-design NNFC/IDEAS & IMS bolometer platforms). Efforts were concentrated on extensive co-design to avoid later double processing work for each of sensor wafer types, ie. IDEAS/NNFC and IMS/XFAB. All of the IZM wafer joint layout has been finished in considerations of both the NNFC & IMS layouts of the bolometer/sensor devices.

In general, following works were performed:

- 200mm GDS full Wafer Layout reconstruction vs. Real wafer – Wafer layout verified (pitch, dicing streets, vs. Chip clustering/shot map on wafer) based on Dummy ROIC wafer (last metal layer & top pass open) delivered by IDEAS (Figure 7)

- GDS Chip Layout: implementation of corresponding process features

- Finalisation WLP Wafer layout vs. Process flows vs. Topologies (monolithic cap etc...) + design freeze.

- Seal ring position: Alignment with IDEAS and IMS for NNFC and XFAB MBA design

- Wafer Lithography and bonding marks sequence

- Getter: marks ok, implementation cross-checked with European industrial Provider

- wafer alignment: (aim: keep the design in all process flows compatible)

- Alignment IDEAS/IMS/IZM for XFAB design (Base/Probe wafer with AI for Pirani MEMS @ IMS)

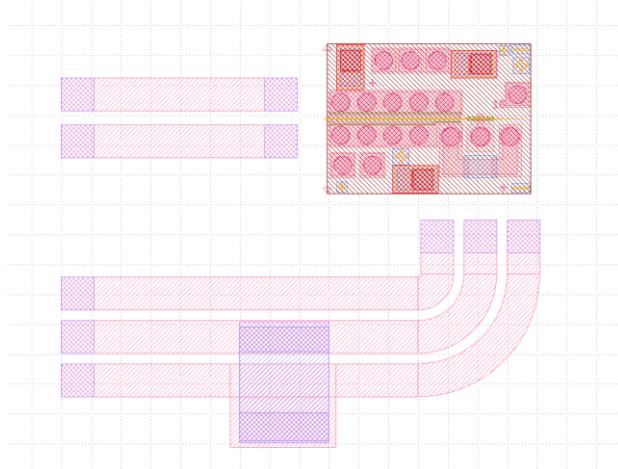

Figure 7: Wafer pre-layout and WLP features

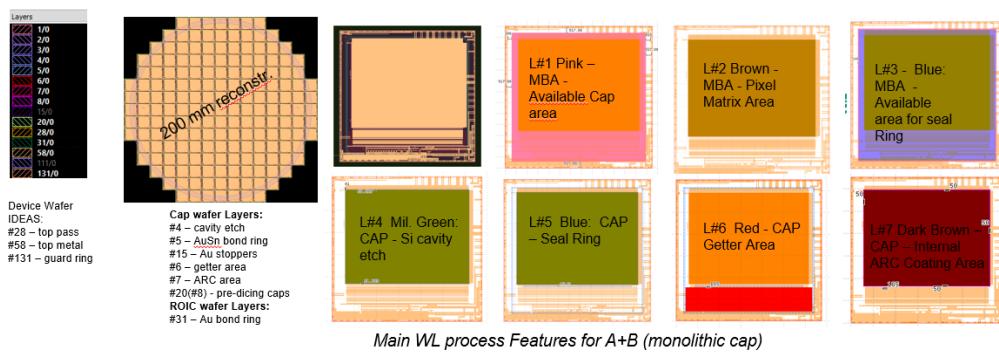

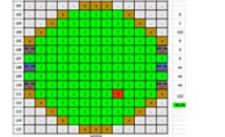

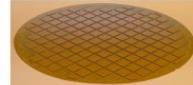

The final wafer layout for WLP is only briefly shown in Figure 8, the entire layout enclosing more than 30 layers. Since the Pirani wafer are conceived on the IDEAS base layout, the WLP layout is compatible for two separate tracks:

- a. WLP of wafer from IDEAS (Norway, MEMS made in South Korea @ NNFC),

- b. WLP of MicroPirani from Fraunhofer iMS in collaboration with USN (Norway).

Figure 8: final layout overview for wafer level hermetical capping of bolometer

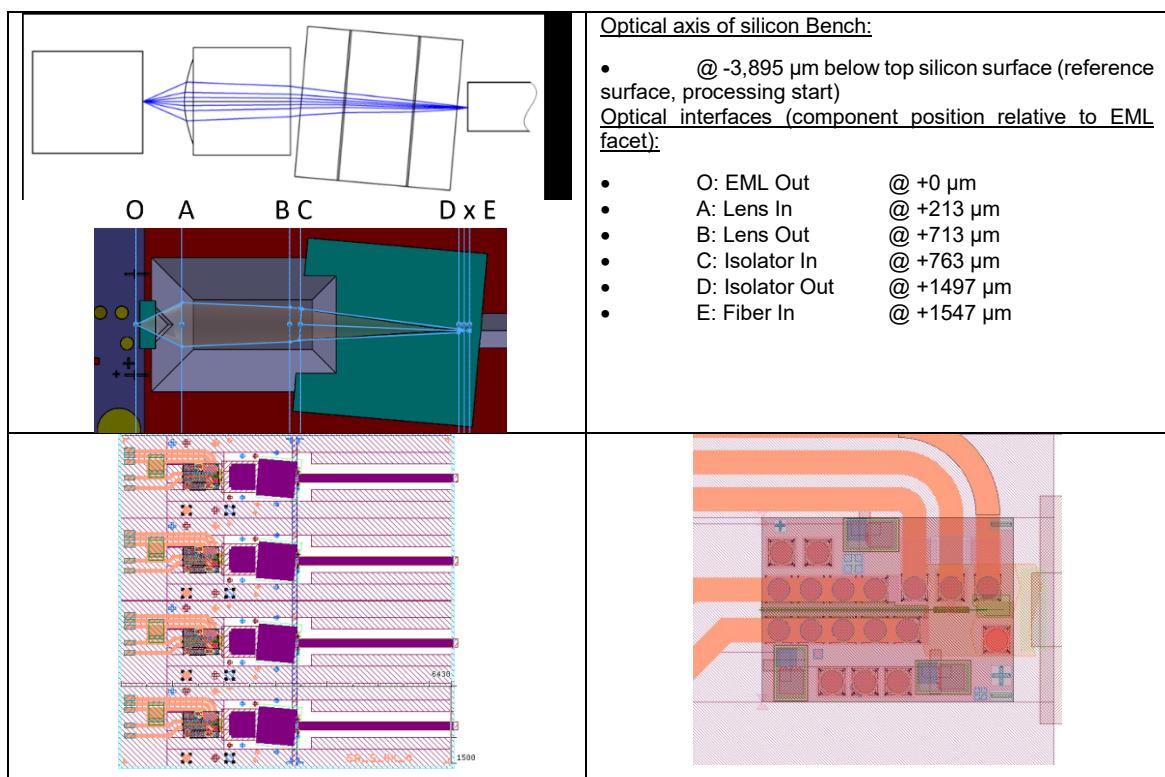

### Task 3.3 UC3 design (Passive fibre alignment for single mode transceivers)

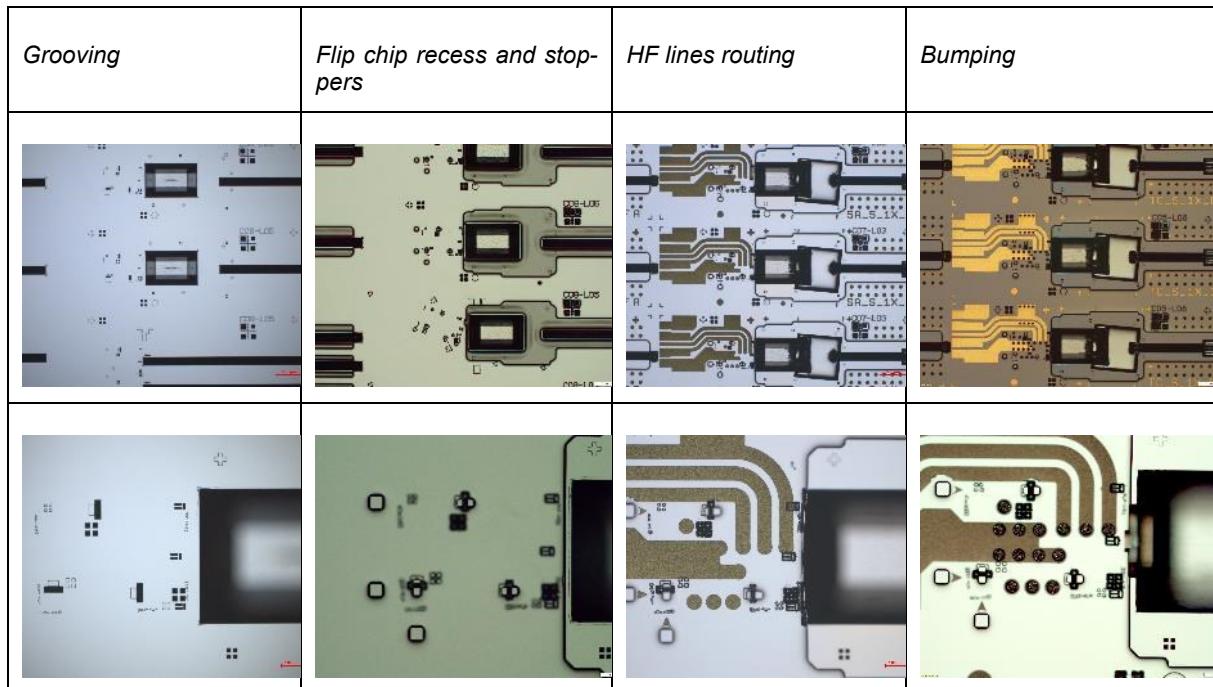

In the task, following layouting works have been done and can be summarized as follows:

- ◀ Design of Si-Bench for 3D passive alignment

- ◀ with V-Groove for alignment of optical elements (lens, fibre), defining the optical axis

- ◀ Si-Microstructuring of 3D-stoppers for passive alignment of EML chip (Electro-absorption Modulated Laser), 200 mm wafer platform

- Reticle Layout AuSn self-alignment: Done (for WP4 P&P and AuSn Solder reflow with solder sustained self-alignment of EML to the mechanical vertical z-stoppers and lateral X & Y-stoppers)

- Reticle Layout precise Au Thermocompression: done (for WP4 Au Thermocompression Bonding with precise flip chip bonder)

- ◀ Design of HF-RDL done (based on HFSS / High Frequency structure simulator)

- ◀ Design for Bumping with Au and AuSn micro-bumps

- ◀ Si bench for machine testing for BESI for thermocompression bonding

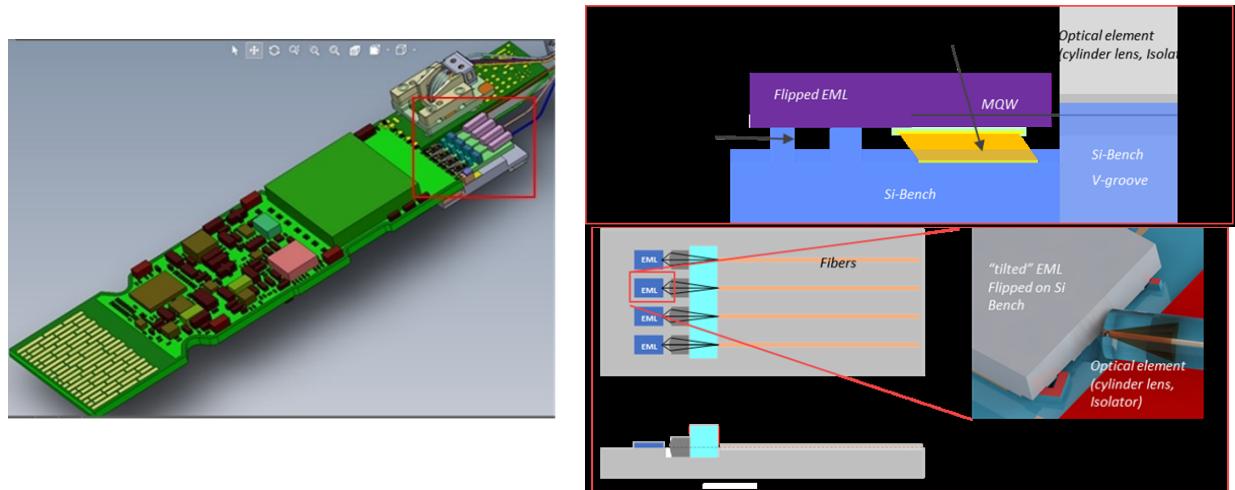

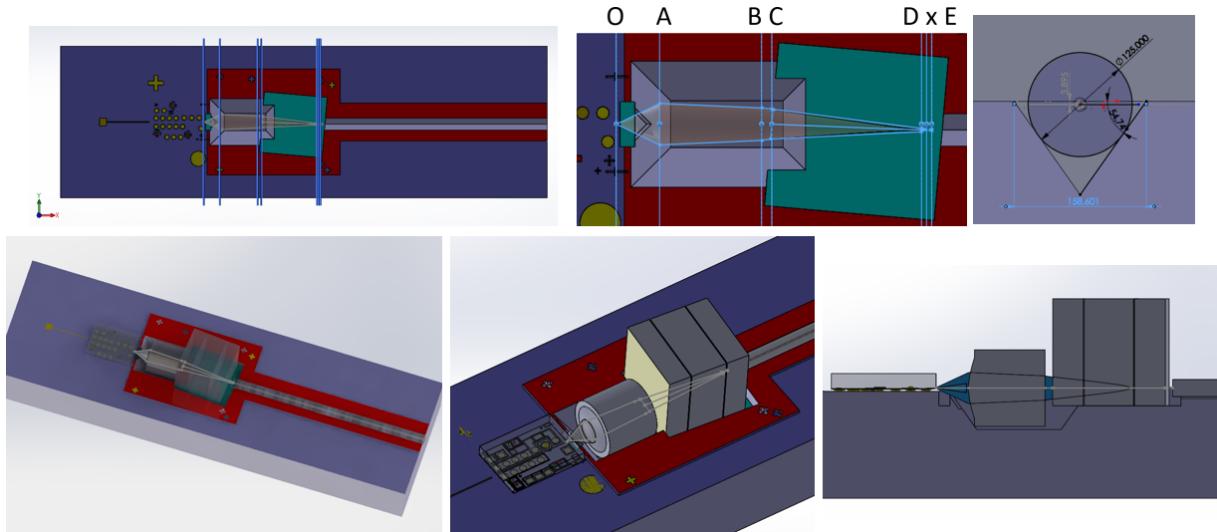

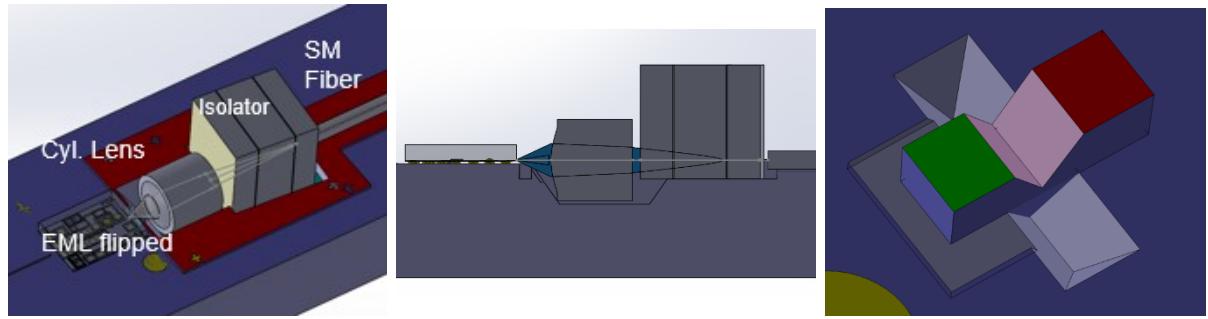

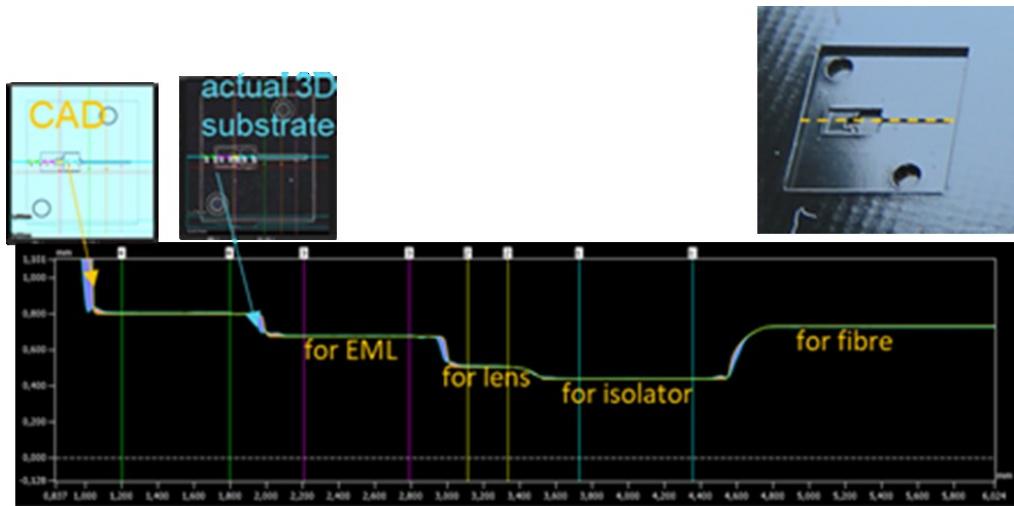

Using 3D-CAD (Figure 9), dimensioning and relative positioning of the different elements/features like the X/Y lateral mechanical stoppers, Z-Spacers (vertical mechanical stoppers), v-grooves, wet etch cavities, have been drawn for 3D representation of the bench taking also into account the beam travel simulated by DPH. Based on those 3D-CAD drawing, the layout for wafer processing have been then extracted.

Based on the overall Silicon bench concept, intermediate test vehicles were also integrated into the wafer reticles with the UC3 silicon Bench for significant testing of the assembly technologies (Flip chip laser with “fiber groove only”, i.e. no lens, no isolator). For both assembly technologies, those aim for different purposes, amongst others flip chip assembly basic tests, fiducial recognitions, simplified optical test after EML bonding for verification of correct final placement of the EML relative to the optical axis as well as metallographic cross-sectioning.

Figure 9: 3D-CAD Si bench, concept, elements, X/Y stopper for self-alignment

Figure 10 gives an insight on the pre-layouting of silicon bench, with the relative places of the optical elements, the features to be etched and the HF-lines to be fabricated onto the silicon bench for driving the modulator embedded onto the EML device after its flip chip assembly. Different variations were gathered, for example using a single lens array or isolator, instead of 4 single elements, however due to the 1.6 mm pitch of single TX-Units it was not compatible.

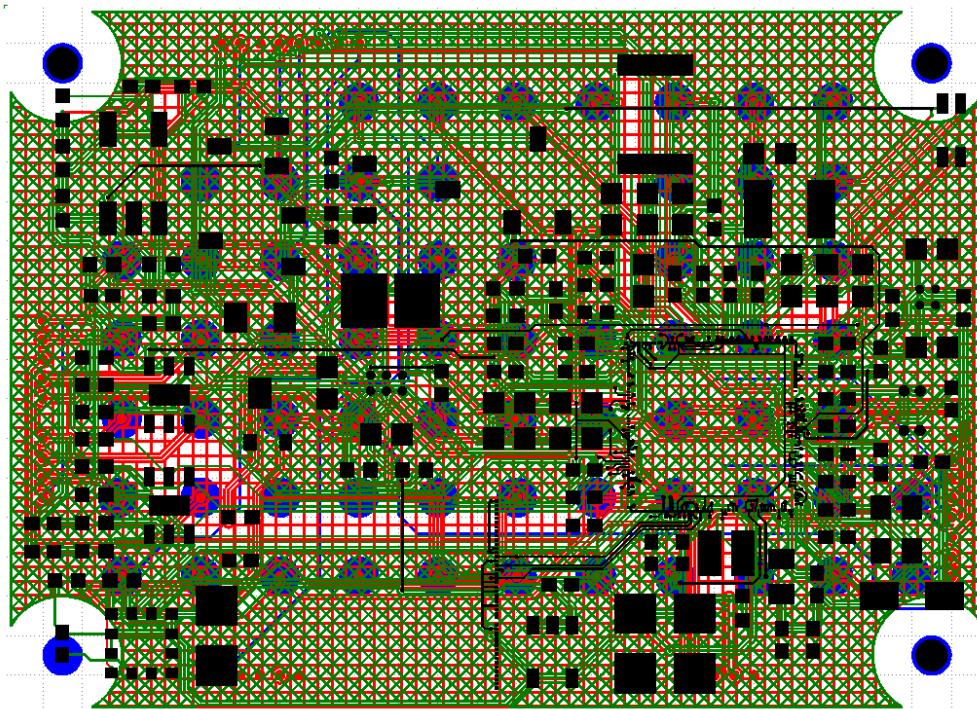

Figure 10: Pre-layout GDS of 4x Channel Silicon Bench for Assembly of single EML (solder self-Alignment, gold thermocompression @ IZM) and left, ‘TCB’ (Thermocompression Bonding @ BESI) and respective view on EML and HF routing, left solder self-alignment with stoppers, right, TCB (HF-routing to be still implemented)

In order to implement variation a base reticle was created, whereon features then were varied to implement sub-variations for packaging (bump quantity, bump diameter, stopper size etc)

The base reticle comprises layouts of different complexity for both chip variant (straight and tilted) arranged in diverse simplified test vehicles embedding:

1. only the laser and bumps for control of shear testing,

2. simple layouts with also 3D stoppers to test the 3D-Assembly,

3. with HF-RDL and fiber grooves to test the passive alignment and perform simplified reliability tests (for example thermo-cycling)

4. and the entire optical bench including all elements in the scope the final demonstration:

- for the assembly technologies at Fraunhofer IZM

- for testing the pick-and-place machine of BESI Austria

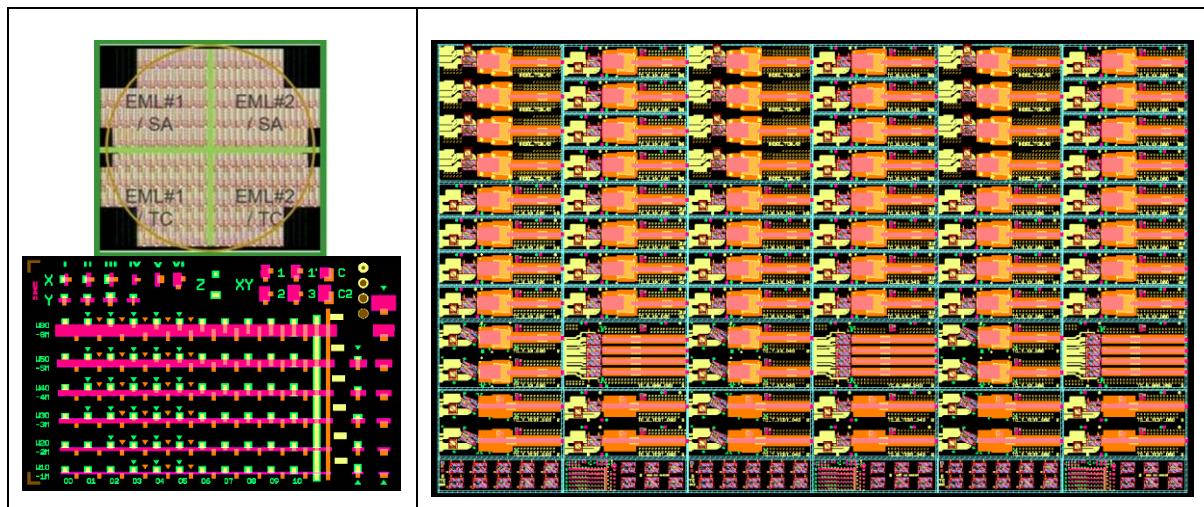

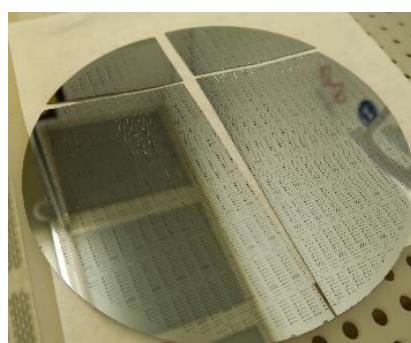

Since the processes involved for the fabrication of the silicon bench are for all the same, apart from bumping, which take place at the end of the fabrication, all the substrate designs for both flip-chip assembly technologies and both EML chips were merged in a single common 200mm wafer layout and repeated in the 4 wafer quarters (Figure 11). This permits a more efficient approach:

- by limiting the number of masks required for processing,

- With an increase of the number of wafers in the process batch and so a increase of test wafers available for WP4 setups

- and consequently limit the risk on processing and adjust in consequence the most promising designs,

instead of having multiple different runs in parallel, with complex lithography works and possible process overload/bottlenecking.

In order to also test the lithography capabilities and the achievable results, an additional test layout has been also conceived and added in a repetitive manner over the entire wafer for the sake of control of process results on silicon microstructuring on slanted structures (created by the Si wet etching) and to get informative results to adjust the layouts of the benches accordingly if necessary.

Figure 11: View on common wafer layout and its partition, the lithography test field and one of the base reticle

The major drawbacks of fusion of all the layout onto a common wafer layout are

1. The wafer complexity is getting very high

2. the quantity of wafer to be processed can become too large and take correspondingly more time for the batch to go ahead and the large increase of variations present on a same wafer.

- 2x Assembly technology

- 2x Laser device variant

- 3x shifted bumps for self-alignment

- 3x different bump diameter for thermocompression

- 4x base layout

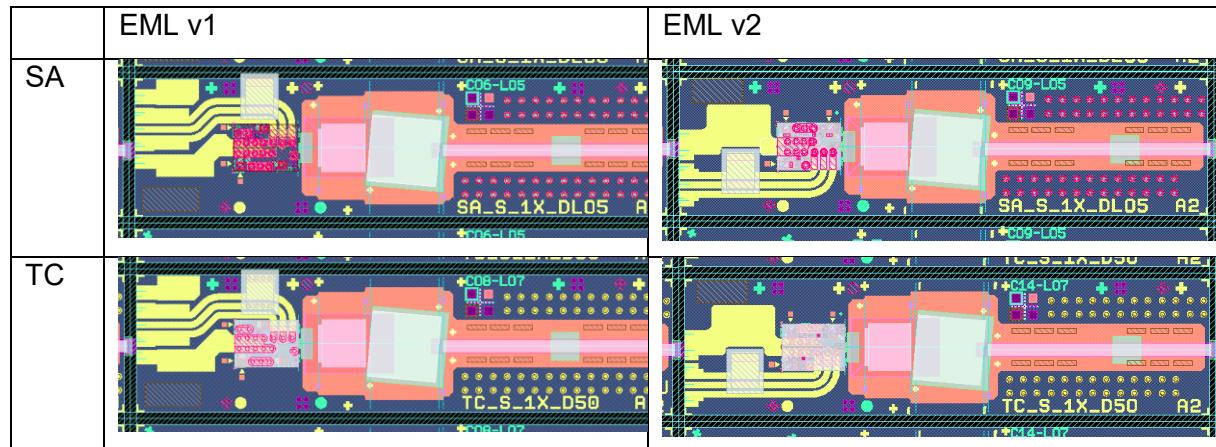

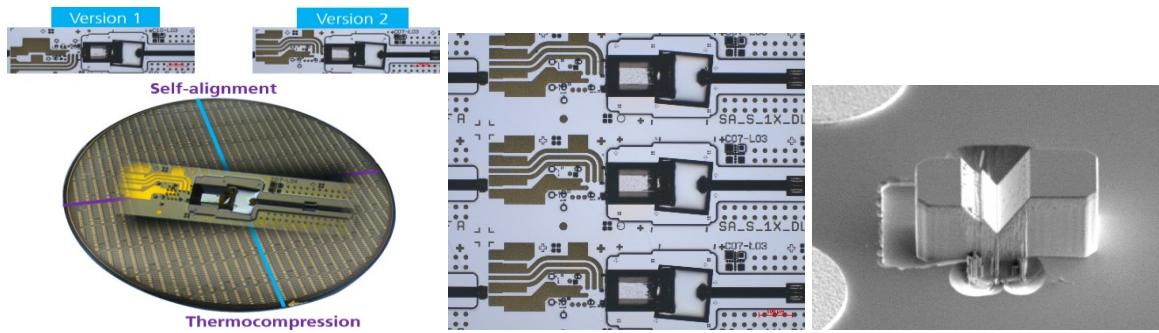

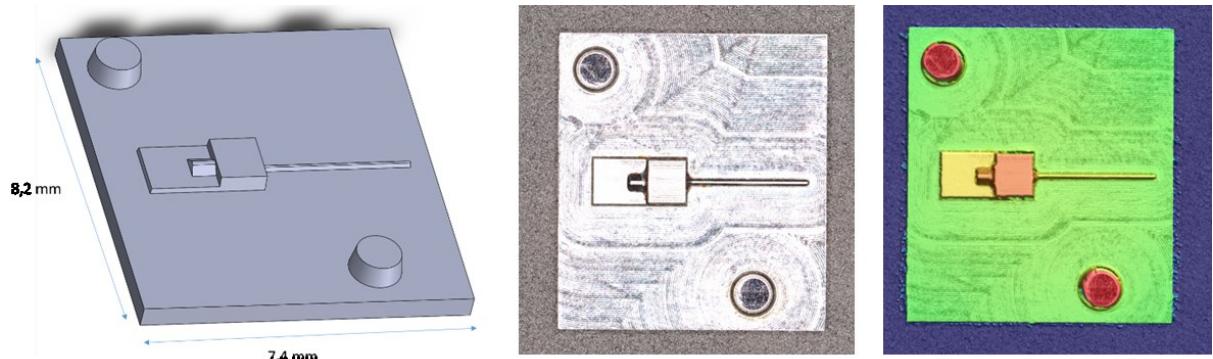

The 4 base layouts of the submounts for the 2 different EML chip versions and for both flip chip technologies (Self-alignment and thermocompression) are reported in Figure 12. The submount is ca. 5.8 mm long and in a 1.6 mm pitch on the wafer layout. Dicing streets are 130  $\mu$ m wide for correct mechanical dicing and clearance to 3D topography.

Figure 12: final base layout of the 3D Silicon submount, for self-alignment and Thermocompression for two chip version (v1, v2) for precise passive alignment of Flip chip laser, Lens, Isolator and fiber for building a Transmitter Submodule.

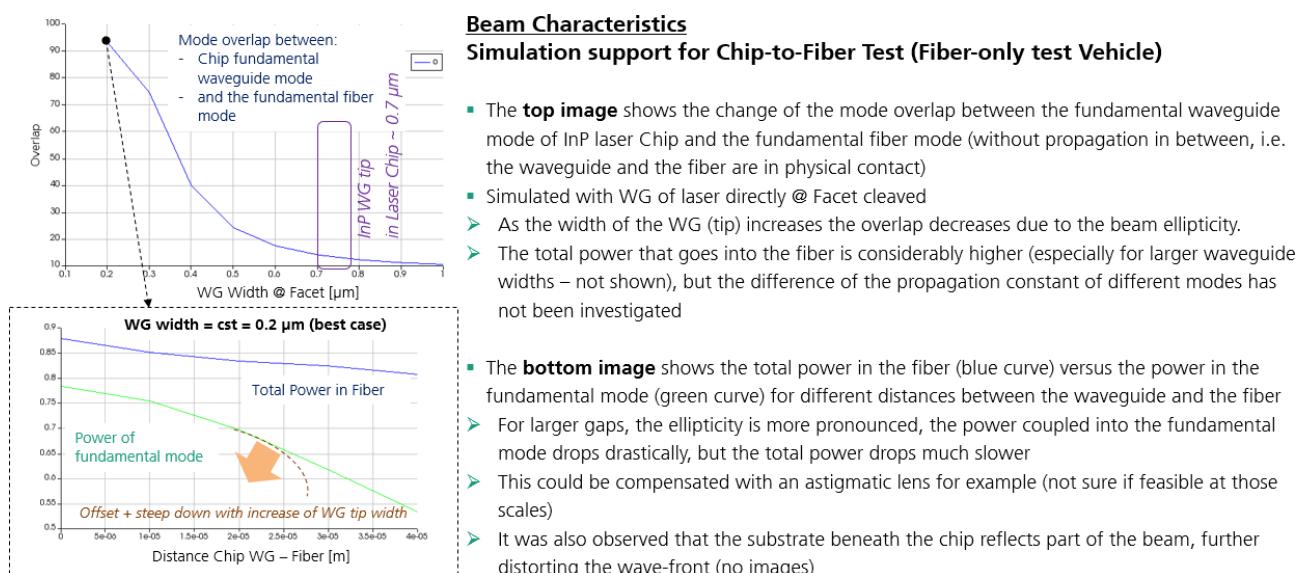

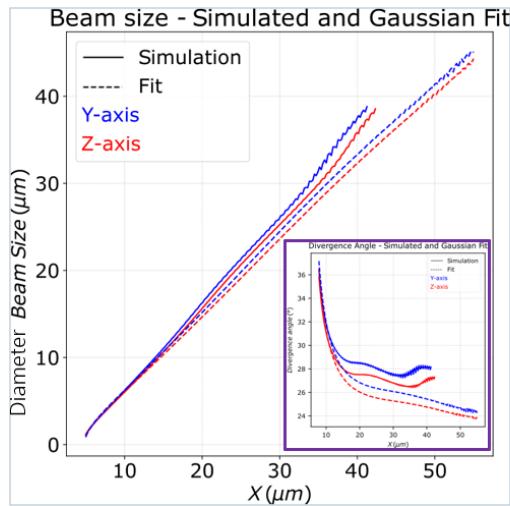

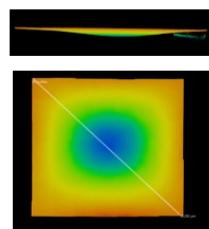

Apart from layouting, optical simulation works were also performed for Chip-to-fiber coupling in order to support / better understand the experimental results obtained (Figure 13) and in the scope of the characterization of TX-sub-module fabricated on 3D Silicon bench (Figure 14).

Figure 13: Simulation support for chip-to-fibre testing (understanding of experimental results)

### Beam Characteristics

#### Spot Size – Divergence (=> Sub-module Dimensioning)

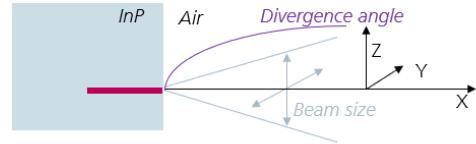

- The fundamental mode of the waveguide in the InP laser was excited and following the propagation inside the waveguide and in air was simulated

- The idea is to observe the beam propagation in free space and validate the characteristics of the lens

- The mode field diameter ( $1/e^2$ ) was found from the simulation results (Simulation) which were also fitted to a Gaussian profile (Fit)

- The difference between the MFD on the two axis show the ellipticity of the beam

- The divergence angle (inset) is max 30deg, so a numerical aperture of 0.5 should be fine

- The aperture of the lens (500um) positioned 200um away from the laser facet is also large enough to capture the whole size

Figure 14: Simulation for sub-module dimensioning

This work supported the flip chip integration on the 3D Silicon Benches, and was necessary in order to better understand the opto-electrical results of intermediate test vehicles with Lasers precisely mounted by Flip Chip on the 3D Silicon substrate and lighting directly in glass fiber (purpose: verification of post bond alignment of laser to optical axis).

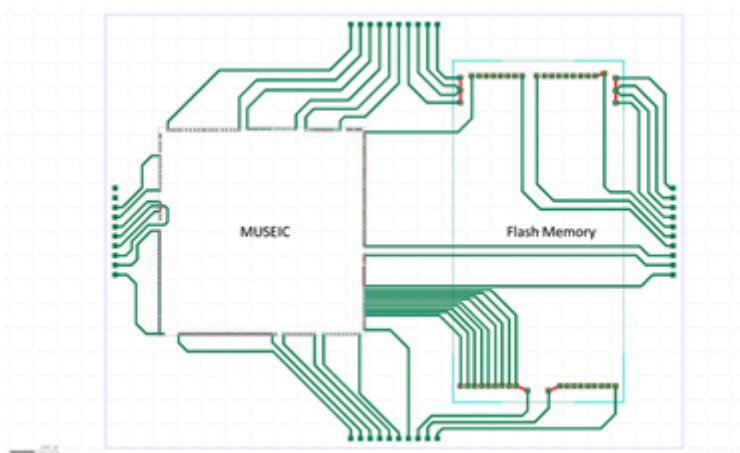

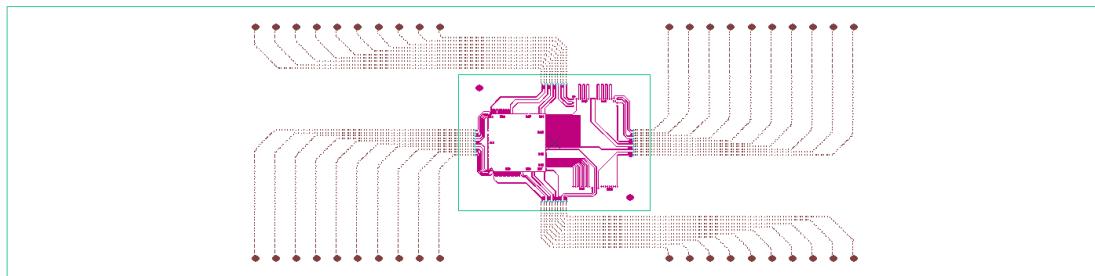

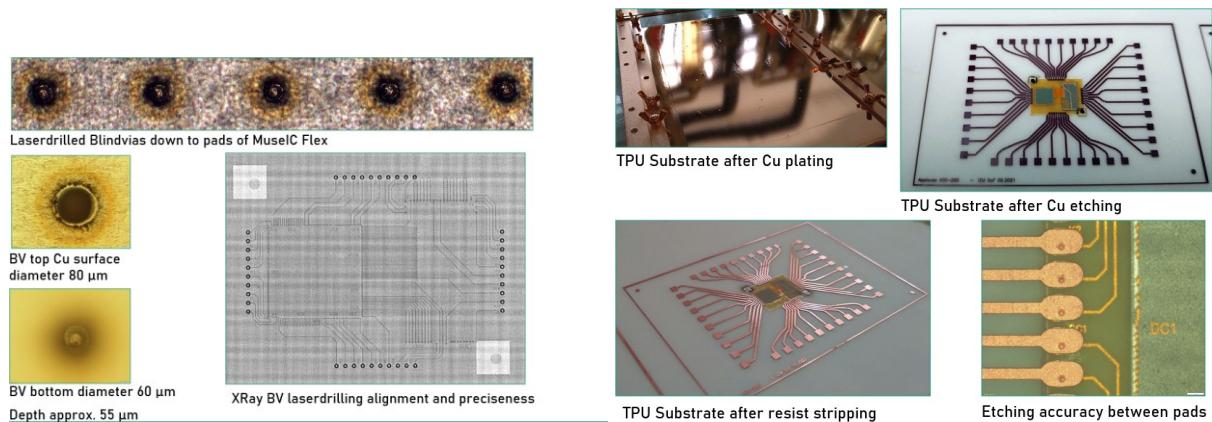

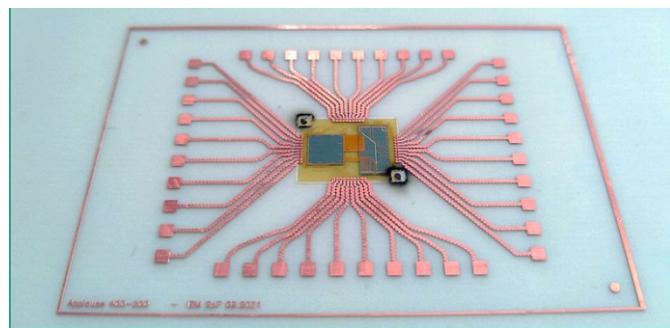

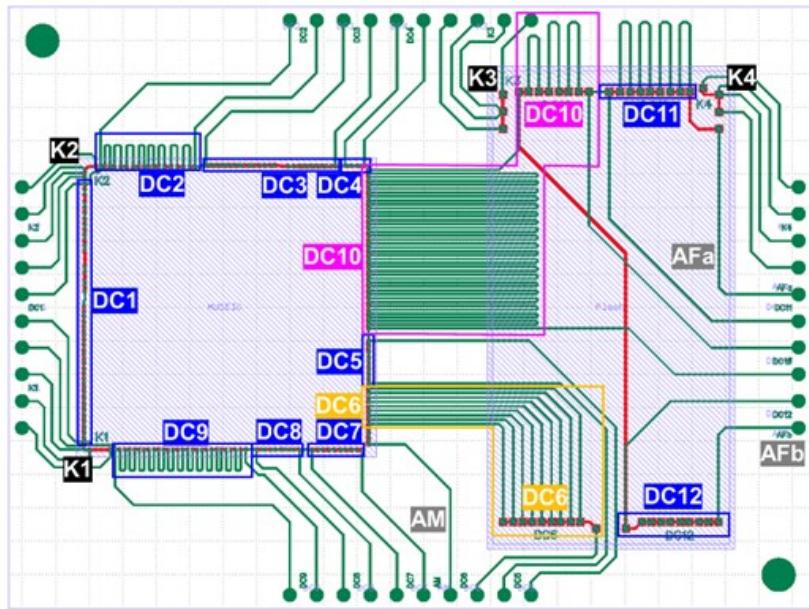

### Task 3.4 UC4 design (Cardiac monitoring system)

#### a. Passive test vehicle

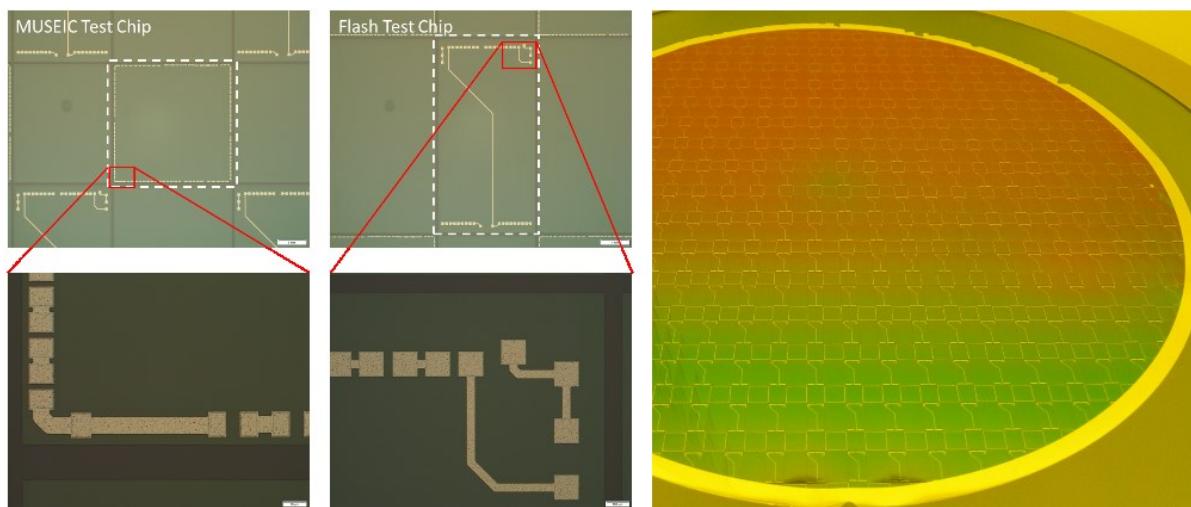

FhG-IZM created, improved and fixed a first passive test layout (Figure 15) for the process developments regarding high density flex fabrication with embedded ICs and flex on stretchable substrate integration. The test layout is based on IMEC-NL's MUSEIC device, which is a SoC available as non-packaged bare die. Due to non-signed NDA and lack of gds2 design data of the SoC, the die pad layout was re-established at FhG IZM based on coordinate list and given pad dimensions from IMEC-NL. Due to limited number of available functional MUSEIC devices, the test layout for thin die embedding into flex included dummy devices based on the layout of the MUSEIC.

The MUSEIC requires a flash memory for data storage. Based on that, the test layout includes dummy devices of flash-memories which had originally also to be integrated into the flex as thin device. Functional flash memory devices had to be procured and could only be used later for the fabrication of the final functional demonstrators (one single wafer available). A simplified overview of the test layout with the MUSEIC and flash memory is shown in the Figure 15. It comprises amongst others fiducials for chip bonding and test structures, especially daisy chains from flex-to-dummy chip-to-flex to verify the interconnect integrity. Due to non-fixed final delivery source of the flash memory, which also need to be available as bare dies, a representative layout of a flash memory was taken out of FhG-IZM layout database to enable the start of the test layout and the fabrication. Both dummy chip layouts, MUSEIC and flash memory, were comprised on one common wafer layout to enable their simultaneous fabrication at FhG IZM.

Figure 15: Base layout of the test vehicle (chip embedding in flex) with interconnections of the flash memory and MUSEIC dummies die.

After the first Die-to-Wafer trials, the design of adhesive layer was also ameliorated. Therefore, the layout was re-adjusted, in order to reduce air enclosure under thin dies after placement

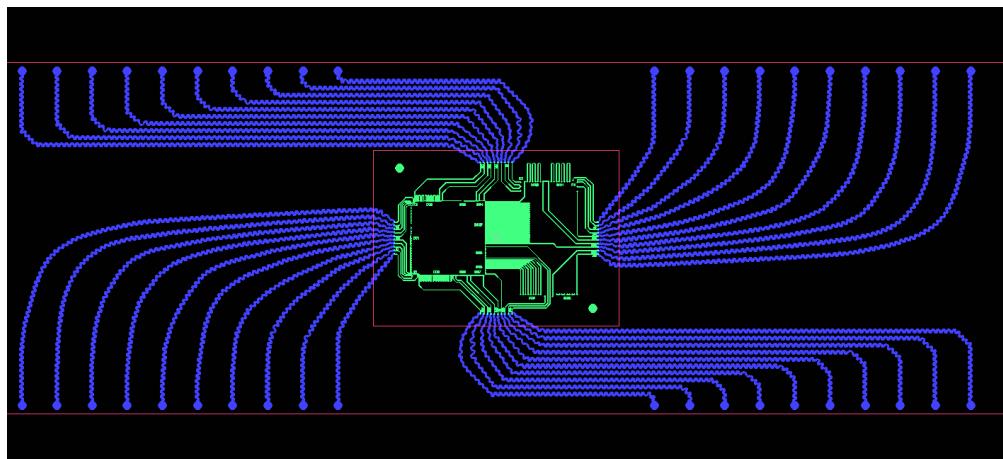

The test layout allows daisy chain measurements over most of the different levels of interconnections between chips, thinfilm flex and stretchable substrate as well as partial measurements for failure location. The Figure 16 shows the wiring in TPU to the chip embedded flex.

Figure 16: Base layout of the test vehicle thinfilm flex with embedded test dies embedded in stretchable patch matrix

#### b. Active test vehicle

Lessons learned were extracted from the 1st flex chip embedding fabrication trial to generate the final layout for functional devices for 5.4.

Fraunhofer IZM has layouted the flex for the functional demonstrator, which carries the MUSEIC the Flash Memory IC, a double LED, an infrared diode, an accelerometer, a voltage regulator, ESD protection devices as well as several passive components. Since the MUSEIC was not available as wafer and only one wafer with Flash memories was available, it was not possible (or had high risk to fail) to thin and embed the active dies, if the approach of extreme thinning and chip embedding would be used.

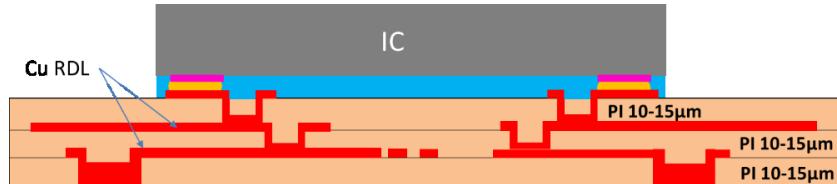

Based on this, the technology approach for the functional flex module was slightly changed to a solution where the chips are not extremely thinned and embedded into the flex. Instead of this, the ICs are assembled flip chip like with stud bumps, together with the other components onto the surface of the functional flex. The flex hosts the same components as the molded SiP version from IMEC-NL with Boschmann. Figure 17 shows the schematic cross view of the intended build-up of the flex. It includes two internal routing layers as well as a top and bottom pad layer. The bottom side pads are used to contact the flex SiP later with the stretchable patch.

Figure 17: schematic cross view of thin film flex with IC component on top

Figure 18 shows a layout view of the flex SiP, which was reviewed and acknowledged by IMEC-NL. The SiP has a total size of 24,6 x 17,6mm<sup>2</sup>. The total expected thickness is 45-50μm.

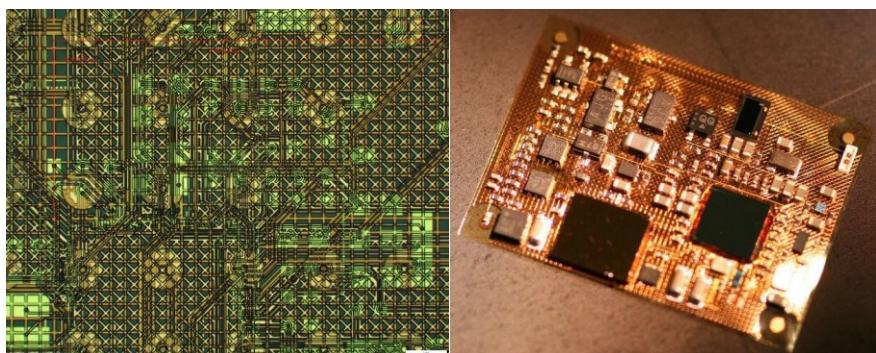

Figure 18: Layout view of functional flex SiP with four metal layers. blue=bottom side pad layer, red=first internal routing layer, green=second internal routing layer, black=top side pad layer

## WP4 Equipment, Processes and Software Components

### Task 4.2 High precision photonic packaging

4.2 a) Test vehicle for high precision bonding & 4.2 b) Development of a Flip-Chip process for high precision assembly

#### 4.2.a) 3D Silicon Substrate Fabrication

The fabrication process concentrated onto a first version of the 3D Silicon Substrates ("WP4 grade") in the scope of generating substrates valuable for performing the 3D precision flip-chip processes. Without 3D-substrates, the Flip chip processes intended in APPLAUSE (mechanical stop on vertical stoppers for flip chip thermocompression, on vertical+lateral stops for flip chip self-alignment) cannot be experimented.

After WP3 Wafer Design fix by summer 2020 and entire process flow definition, first process masks were ordered. The fabrication necessitates basically 7 masks:

- 1 Vernier for 100 crystal orientation, (Wet Si etch, Hard Mask)

- 2 V-groove etching, (Wet Si etch, Hard Mask)

- 3 z-stopper level, (DRIE Si etch -4 µm, Spray PR Mask)

- 4 Flip chip recessing (DRIE Si etch -31 µm, Spray PR Mask)

- 5 Isolator recessing (DRIE Si Etch > 75µm, i.e. 110 µm, Spray PR Mask)

- 6 Routing (gold electroplating 3 µm, Spray PR Mask)

- 7 Bumping (Au 24 µm, AuSn, Spray PR Mask)

The wafer layout is divided in 4 quarters dedicated to different technologies, the upper part being designed for assembly with solder driven self-alignment, the second half being for gold thermocompression. The left part is designed with the first EML chip version of ALMAE, the right part for the EML version #2.

The merge of all designs is for synergic convenience and possibly to catch up time-loss due to COVID-19 impact and limit the work spread by multiplying process runs with the complex process flow due to high topography. The merge is justified since basically the fabrication of the Si-bench for both assembly technologies differs only by the last process block (bumping). The merging in a single wafer layout of the different designs allows more robustness and flexibility regarding risk mitigation, more wafers being processed in the same batch.

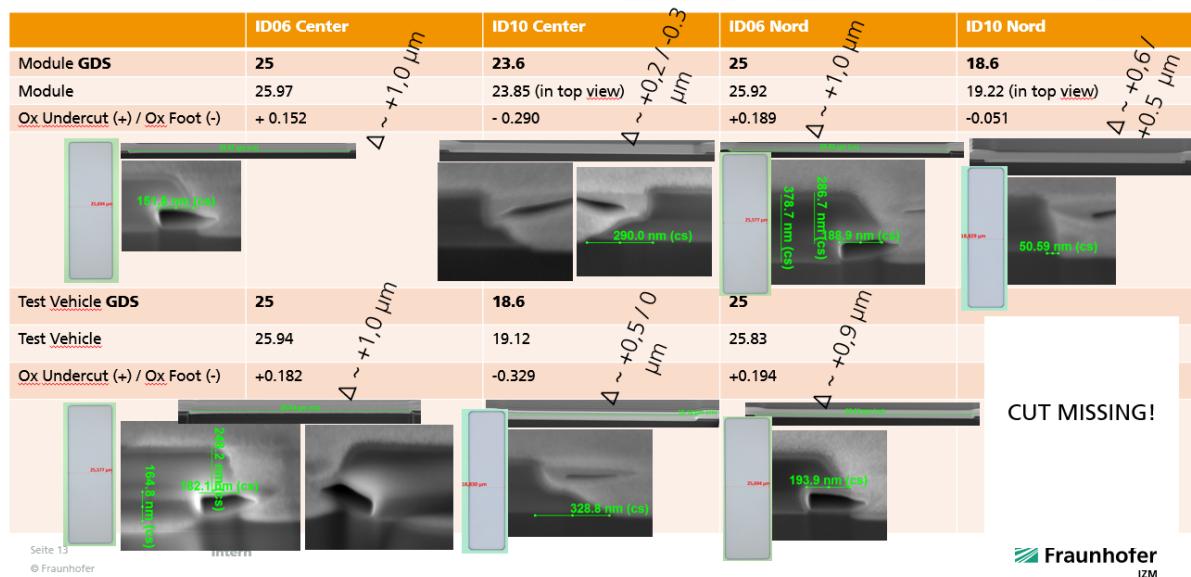

#### A. Silicon Wet-etching

In 2020/Q3 process work has been started on Si-Bench in the frame of WP4. First wet etching process were set and done with the correct features sizes, first on 200mm monitor wafers (WP4) then onto high resistivity base wafers for WP5.

1. Wafer Orientation to <100> crystal direction

2. and wet etching of V-groove structures down to 270 µm nominal depth (for 500µm cylinder Lens) were performed.

However, it appeared the hardmask undercut by the etching process was too "pronounced" (+3µm deviation vs. target) leading to larger etched widths than expected and even to a merge of nearby delicate structures like some fine etched fiducials (not enough clearance between).

This would make the wafer unusable for WP5 in regards of the envisioned submicronic alignment, with a shift in Z of the fiber as well a shift in X and Y of the contact points as designed, leading to imperfectly aligned optical parts.

Therefore, most of the relevant features of differing sizes (V-groove of Fiber, V-groove for lens, V-grooves for stoppers, test v-grooves) were manually measured for highest precision on two wafers before and after hardmask removal in North, South, West, East, Center to verify the undercut homogeneity on large (lens, fiber grooves) and small (stoppers) etched structures.

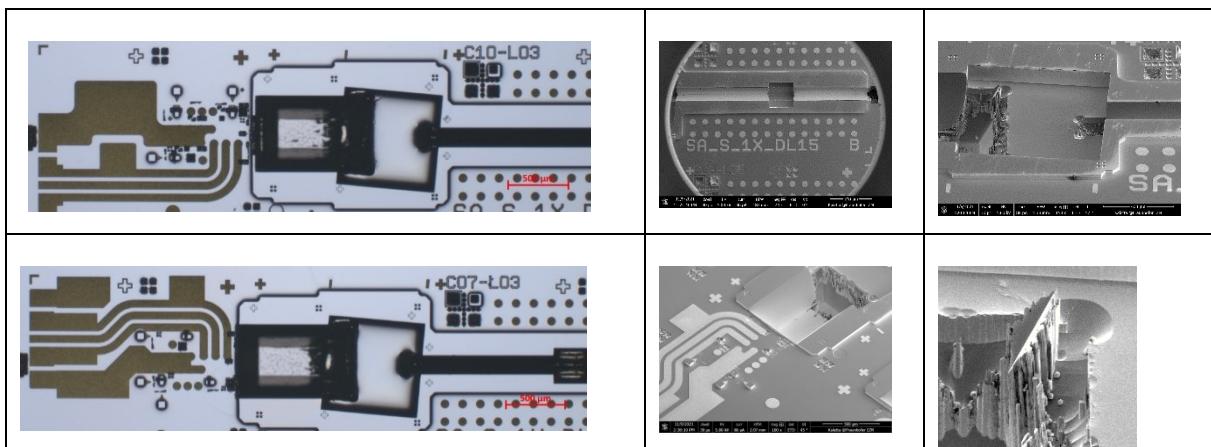

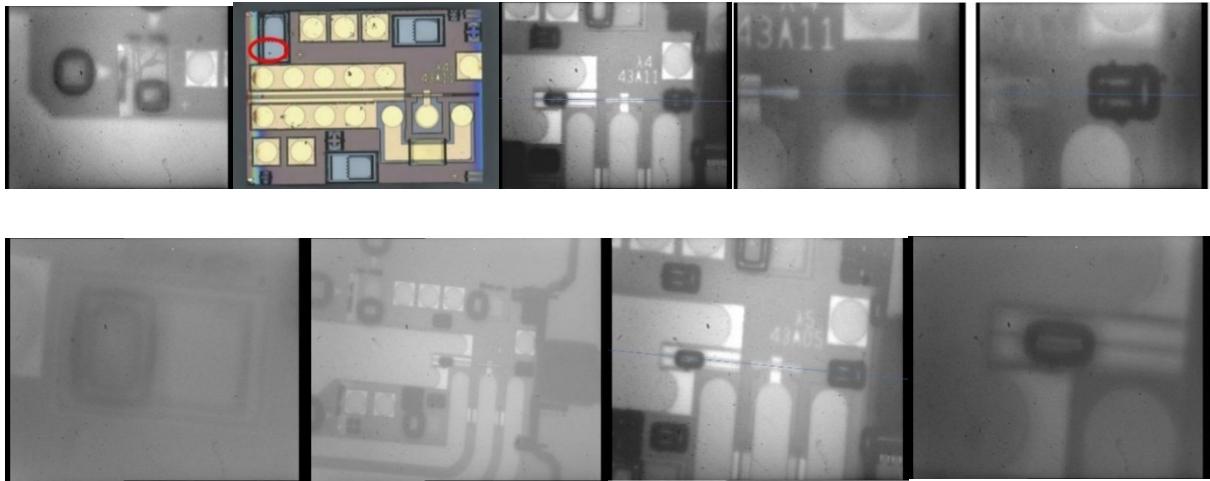

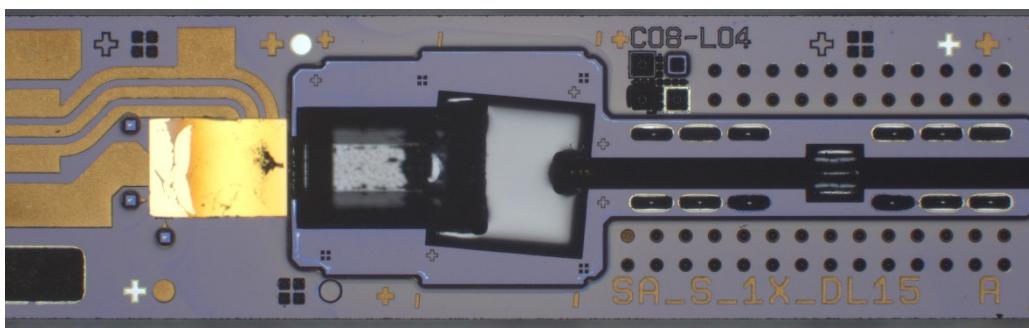

Figure 19: Synergic wafer layout compiling 2 flip-chip assembly technologies (SA- AuSn Solder Self-alignment; TC: Au Thermocompression) for 2 laser device versions. Silicon photonic bench after deep wet etching of the 200mm Silicon wafer

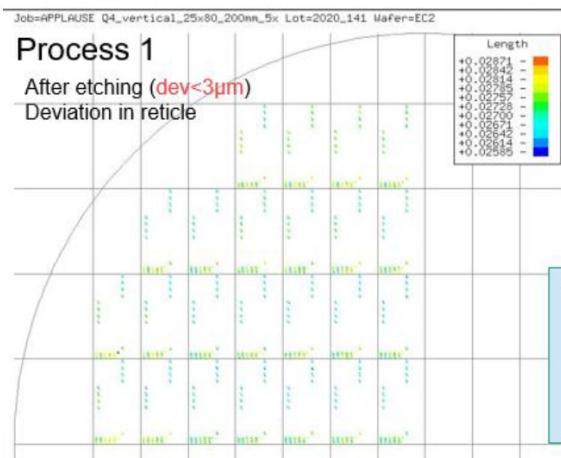

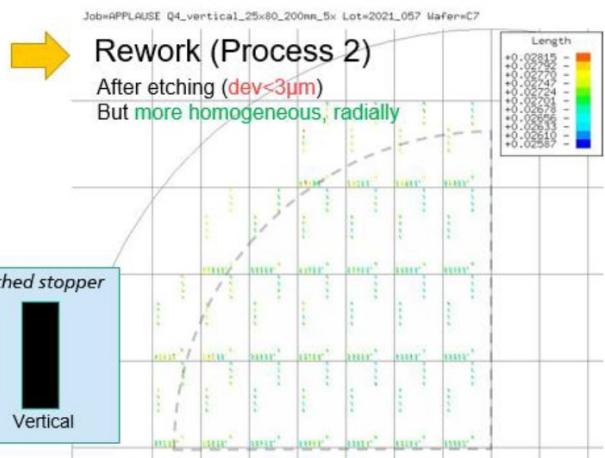

Based on this, a corrected/compensated layout was generated. Since all wafer were scrapped, a new wafer batch had to be restarted from beginning, also with high resistivity silicon (expectation of higher HF performances of the bulk material), to improve the feature size below 1 $\mu\text{m}$  deviation, as a "WP5-Grade" version of the 3D-silicon bench (Figure 20). The relaunch included also the identification of the correct (100) crystal orientation using wet etching of precise nonius features.

The new mask performed very well on monitor wafers by end of 2020, all structures deviating only by ~0.2 to 0.5  $\mu\text{m}$  to the desired values. This process was transposed to the WP5 wafers for final demonstration.

Using an automated inspection tool (limit of tool resolution ~ 1  $\mu\text{m}$  due to pixel/digitalisation), a precision under 3  $\mu\text{m}$  in width (1.5  $\mu\text{m}$  one side) over the 200 mm wafer area and under 1 $\mu\text{m}$  (0.5  $\mu\text{m}$  one side) in 150mm wafer core could be reached for this high resistivity wafers (T5.3.2), assessed by manual cross-control with light microscopy measurements.

## 2020\_141 / Monitor HM open - Comparison

Monitor Topo Wafer

ID06 : Old Mask => One of first wafer processed (Sep20) – Tapas HM Open Process

ID10: New Mask (2x -3.2 $\mu$ m compensation) => processed mid-Nov20 – Pete HM Open Process

Wafer 2020\_142 / C2 , vertical: After etch

Wafer 2021\_057 / C7 , vertical: After etch

Figure 20: Hard mask process evaluation (top), resulting in improvement of feature size deviation <1  $\mu$ m in 150mm wafer core of the 200 mm Si bench wafer (bottom).

### B. silicon dry etching

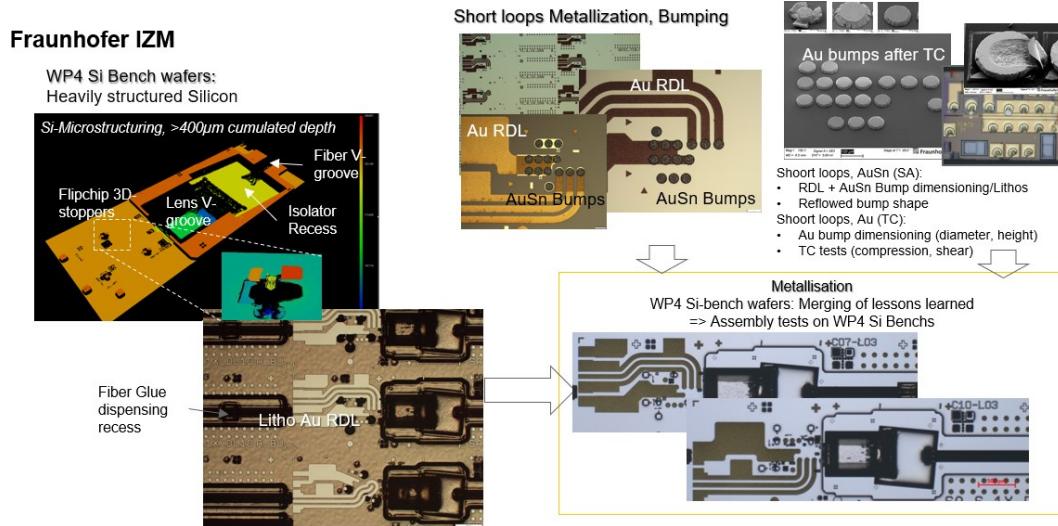

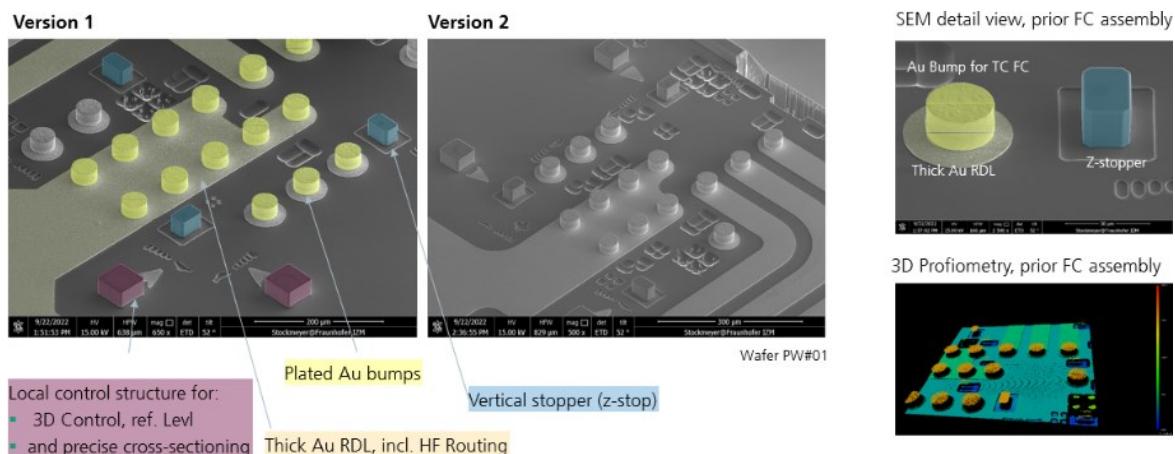

Next steps was first the setting-up of the dry-etch microstructuring (micromachining) of the silicon using lithography and intensive deep DRIE processes (3x, one after another with different target depths) on already challenging high topography wafers (due to deep v-grooving). Processes were individually tested and combined in a fabrication flow. Metallisation tests (RDL, Bumping) were also tested in parallel, first on planar wafers, for rough setups/short loops (Figure 21).

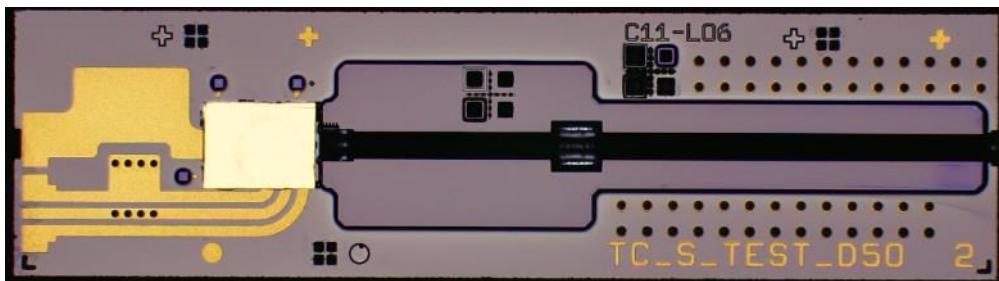

The shortloop bumping materials were further exploited to verify the bump compression with 3 different bump diameters (D20, D40, D50), to characterize the HF routing and generate first flip chip assembled InP laser onto the HF routing, inclusive 50 ohm decoupling resistor (@ March 22), and provided for characterization (Figure 29). This aimed to perform basic DC and HF characterization of the InP laser after flip chip.

Figure 21: Si deep etching/full microstructuring, metallization tests (routing bumping) and combination of boths

- Done: Si Deep Microstructuring (Figure 22), with all structures needed (Figure 23), basically

- o Z-stop level

- o Recess of flip chip area, with formation of stoppers

- o Light path Open and recess for isolator

- Done: Metallization of 3D-structured silicon bench (Figure 24)

- o Thick gold of 3 µm, for the signal lines, High-frequency

Figure 22: WP4 Silicon Bench, recess of isolator and light path open: lithography on high silicon topography (left), after dry silicon etching (center) and surface desoxidation (right)

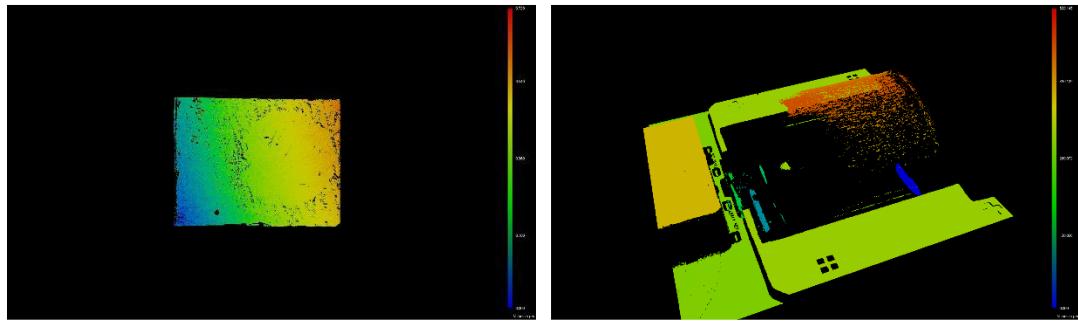

The resulting 3D structure is illustrated in Figure 23 with the CAD schematic of principle of the targeted SiBench. By means of light profilometry it is basically possible to inspect the resulting highly complex structure.

Figure 23: 3D light profilometry measurement after Silicon structuring (Left) and CAD of targeted Bench (right)

### C. 3D Silicon Substrate Metallisation (Au RDL, Bumping)

The next major task was the metallisation of deeply-micromachined Silicon wafers for routing. A thick electroplated gold was retained, to be compatible with III-V lasers (avoiding any possible Cu poisoning), for HF transmission and to offer enough section (i.e. thickness) for power feed, in comparison to thinner AlSi. The routing was executed by semi-additive process using electroplating of 3 µm thick gold HF-RDL (nota: for power feed, 6µm was by UC owner envisioned but jeopardizing the overall topography tolerances) before moving towards final bumping for both passive alignment bonding scheme:

- Gold bumps for flip chip thermocompression, by means of a high precision bonder (vision-system assisted x/y positioning) for gold thermocompression with z-defined mechanical stoppers on

- and Gold-tin Bumping for flip chip self-alignment, by combining “unprecise” pick-and-place and solder driven self-alignment as well as

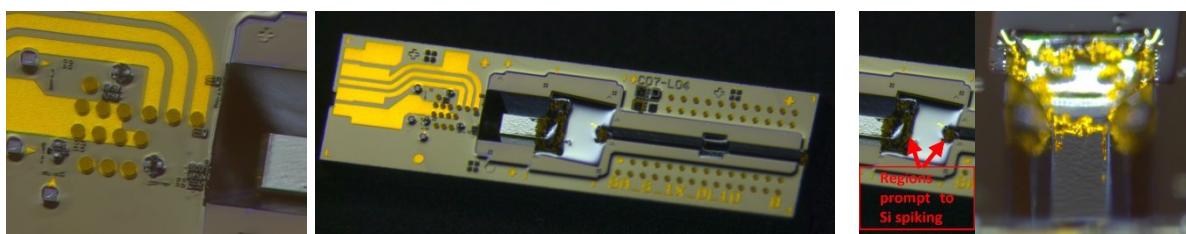

The RDL metallization process could be successfully transferred on the 3D silicon bench wafers of WP4 grade (process developments) as illustrated in Figure 24 / left.

Figure 24: Left: Overview pictures (light microscopy) of Silicon bench after thick Au RDL metallization (for EML version 1 and version 2 of ALMAE), center: SEM views of fiber groove with glue recess (top) and lens groove with RDL (bottom); right: SEM views of 5° tilted isolator recess (top) and magnification on silicon spiking (bottom)

Figure 25 and

Figure 26 give further insight on the fabricated 3D-Si Benchs.

Figure 25: for Fabrication status of 3D Si Bench, 8' Wafer, with example of a 3D-Stopper (here for flip chip self-alignment in vertical position on flat and lateral position on slanted wall)

Figure 26: SEM views of 3D silicon bench with Au bumps

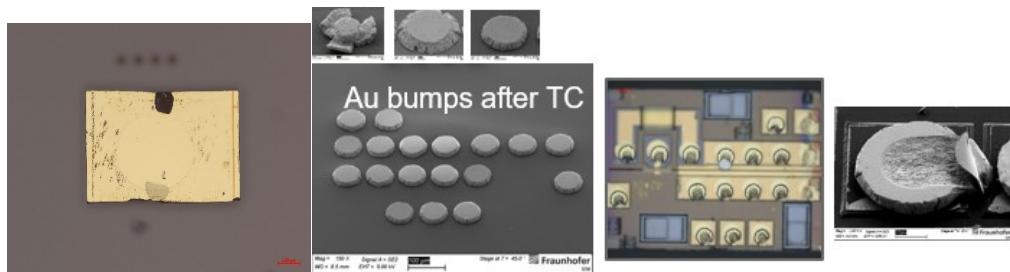

Despite technical issues between Silicon Structuring and metallization, with Si Spikes in Isolator recess pointing out of the photoresist and being then electroplated, thus leading to additional delays (apart from COVID-19 Frame), a first generation of 3D SiBench could be fully completed End March 2022, at least acceptable or even in the target in regards of the Au bumping height:

- for thermocompression flip chip experiments at FhG-IZM

- and process developments for optic assembly at BESI-AT (due to withdrawal of DPH, originally in charge of optic assembly and testing).

Dedicated substrates were also delivered to BESI-AT within this 1<sup>st</sup> generation, substrates having been specifically designed for their bonding equipment developed in APPLAUSE and additionally integrated in the wafer layout.

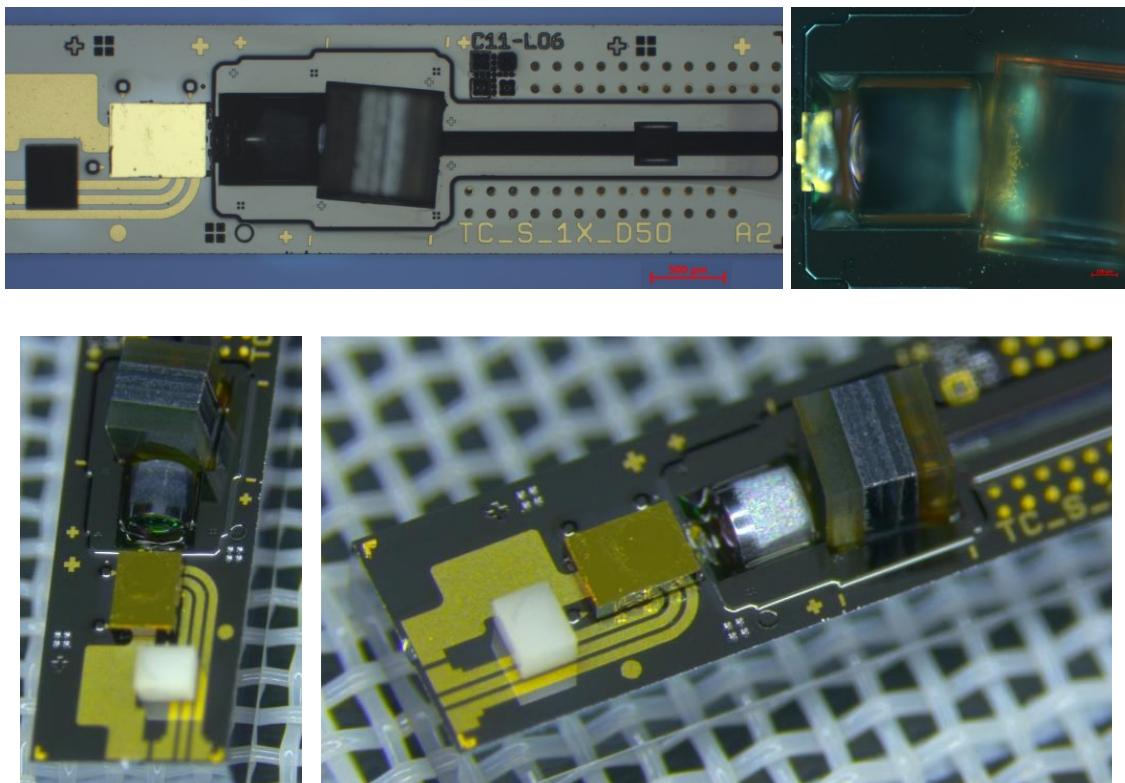

Figure 27: example of a fabricated 3D Si Submount after wafer level processing (Nota: design Self-alignment, no bumps for 50 ohm resistor included, studbumps are here additionally used).

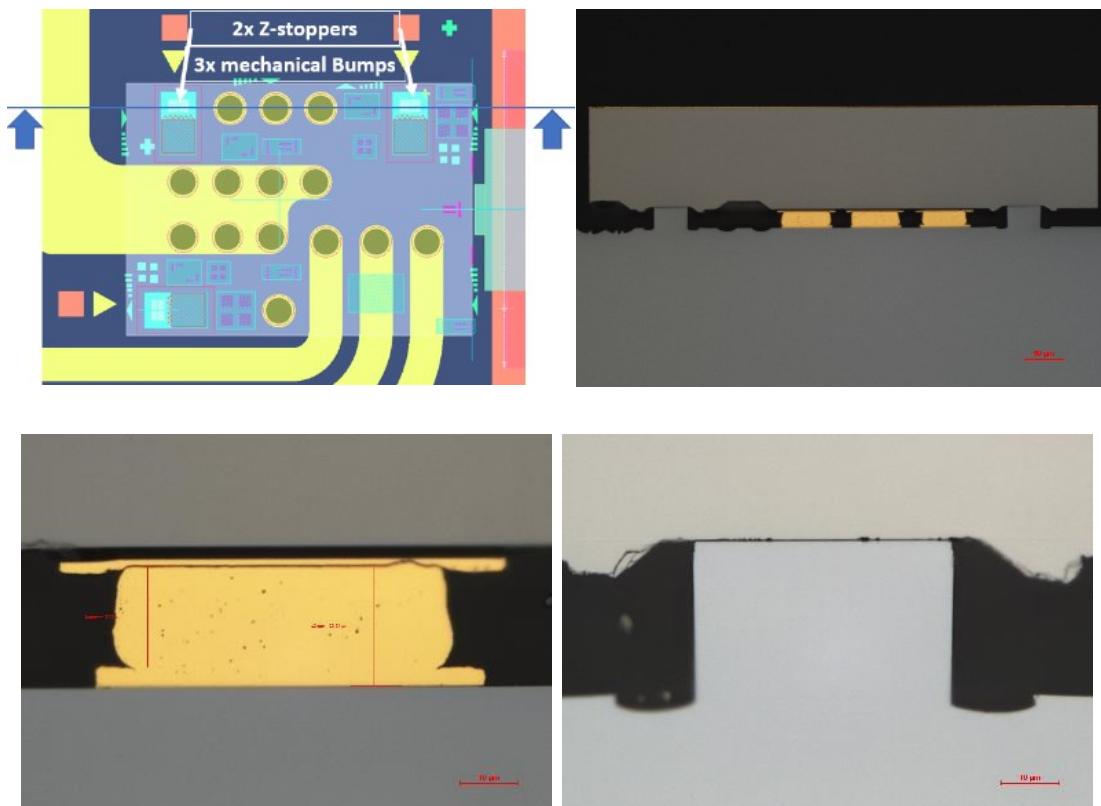

#### 4.2.b) Development of a Flip-Chip process for high precision assembly

##### A. FC Thermocompression (TC)

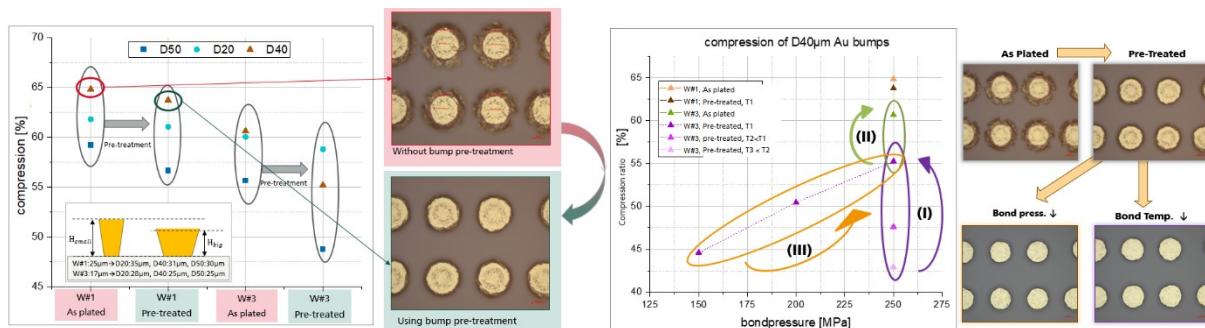

Using short loop wafer (ie. without stoppers), the mechanical behaviour of the Au bumps has been first studied in order to correctly size the bump needed for the thermocompression process in the forefront of the fabrication of the 3D Si Submounts. Following points were investigated:

- Au bump deformation behaviour and bump shaping/dimensioning vs stoppers (Figure 28)

- Shear tests, regarding flip chip robustness (see also Figure 119)

When bumps are directly used “as plated”, they tend to flake with shell detachment, leading to a risk of electrical shorts between two adjacent bumps. Adding a pre-treatment of the bumps prior flip chip bonding permits to resolve this issue. The buckling and barrelling remain limited even by high deformation. The effect of the pre-treatment is a displacement of the maximal deformation by around -2 to -5%, the bump being less deformed. A diminution of the bond pressure from 250 to 150 MPa reduces the maximal deformation by 10% , as well as a diminution of the bond temperature.

Figure 28: Testing of thermocompression behaviour of electroplated gold bumps in different diameter and height combinations (D/H - D20/H35 & 28  $\mu\text{m}$ , D40/H31 & 25 $\mu\text{m}$  and D50/H30 & 25 $\mu\text{m}$ )

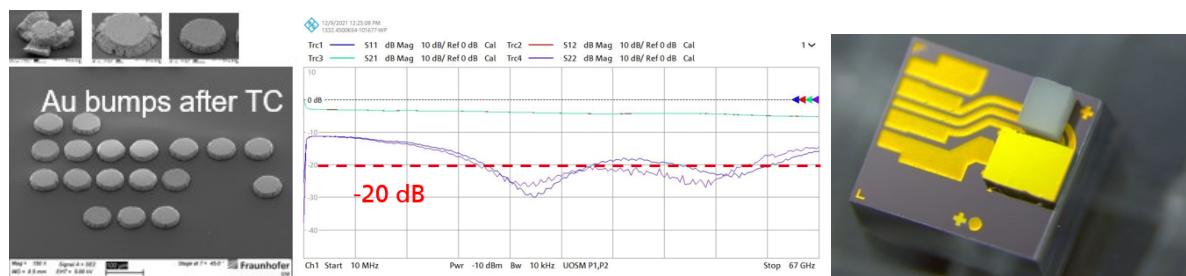

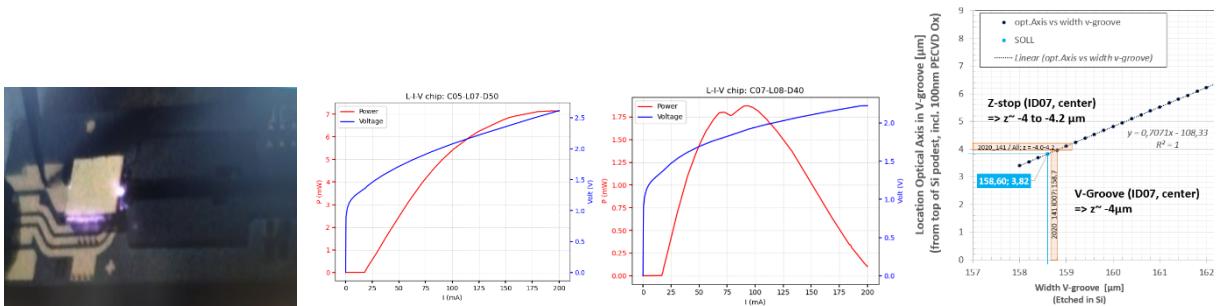

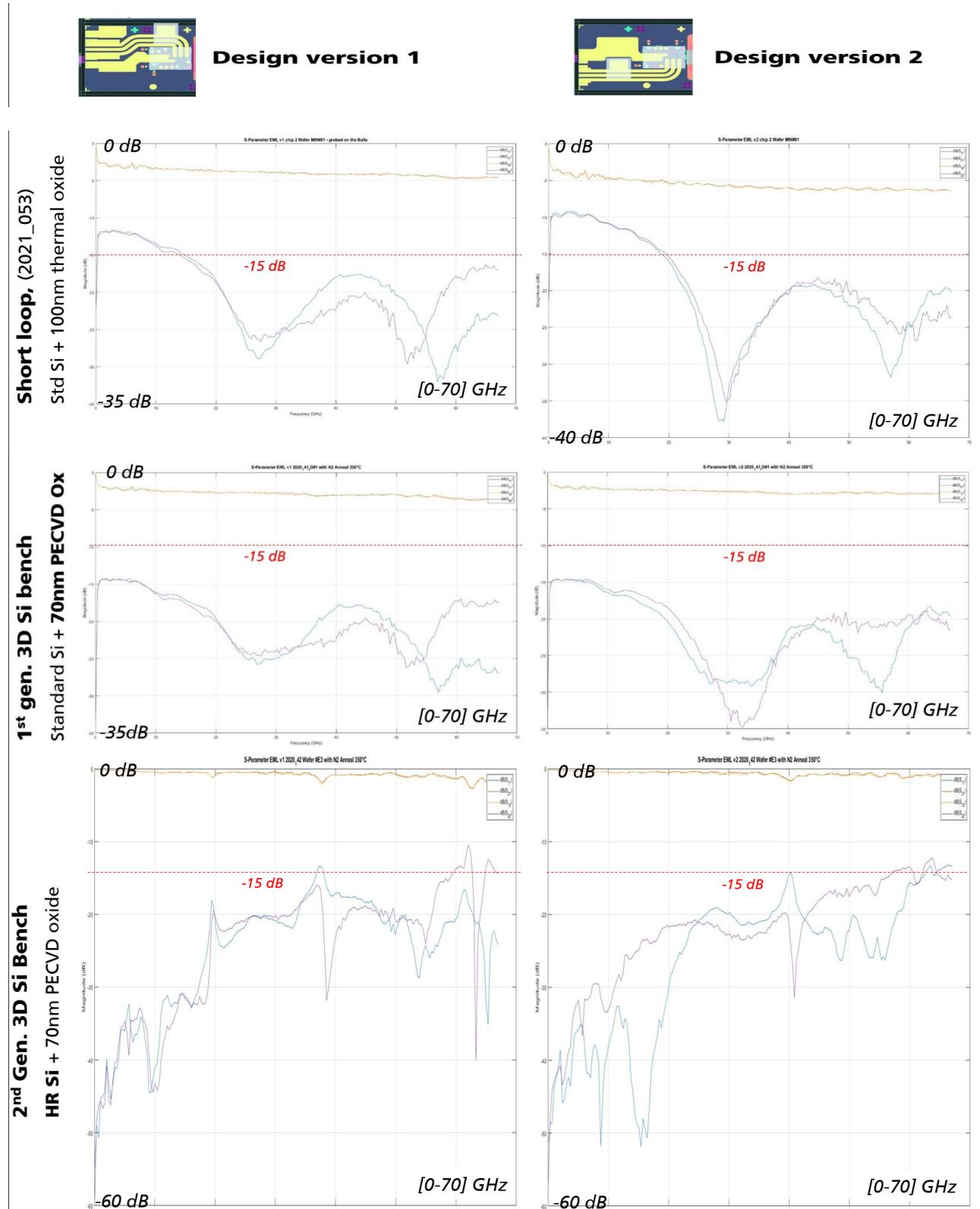

On short loop parts made of standard Silicon (resistivity  $\sim 50 \text{ ohm.cm}$ ), the thermocompression, the HF behaviour and the laser were tested (Figure 29). HF behaviour of the gold lines with standard silicon as base material and 100 nm thermal oxide is in the range of simulated values.

Figure 29: Evaluation of bump thermocompression and HF routing ; shortloop flip chip samples for FC characterisation

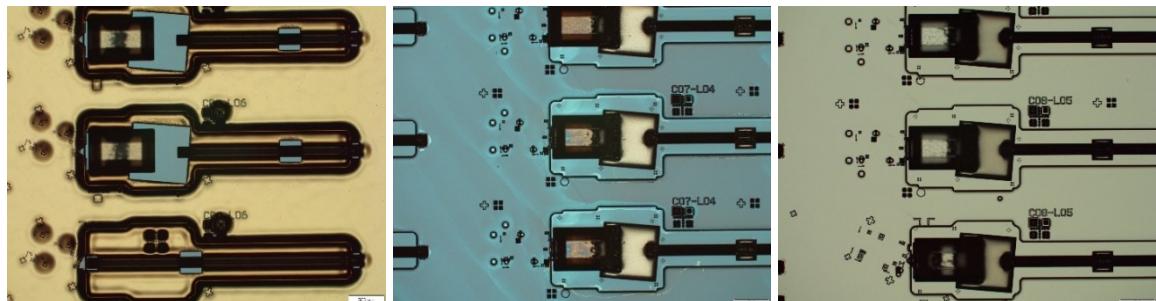

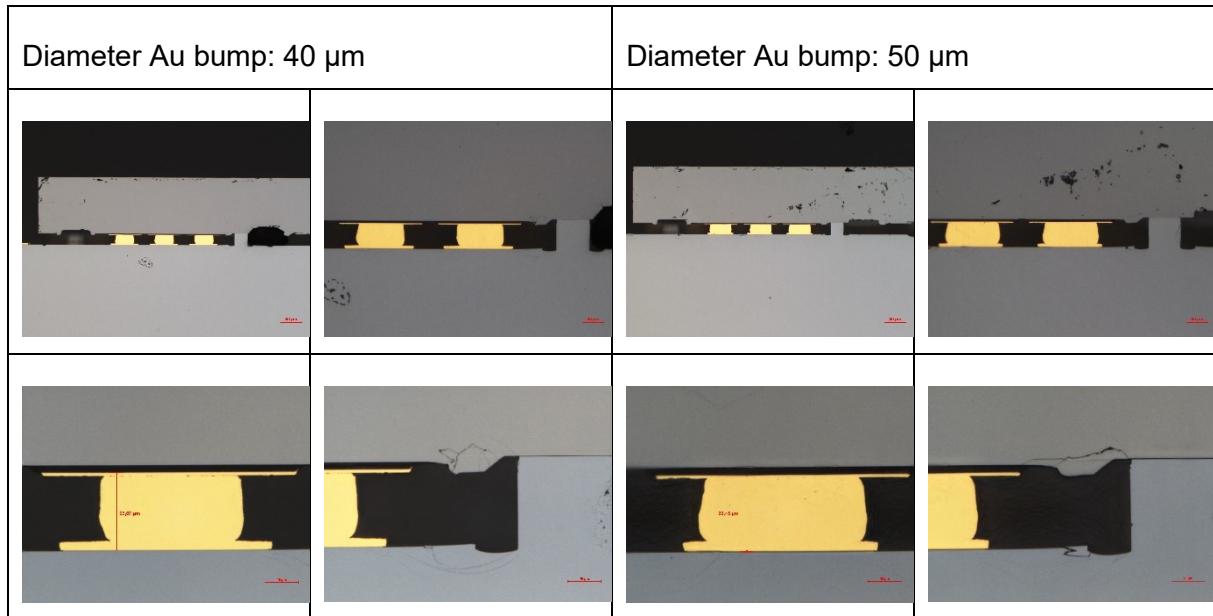

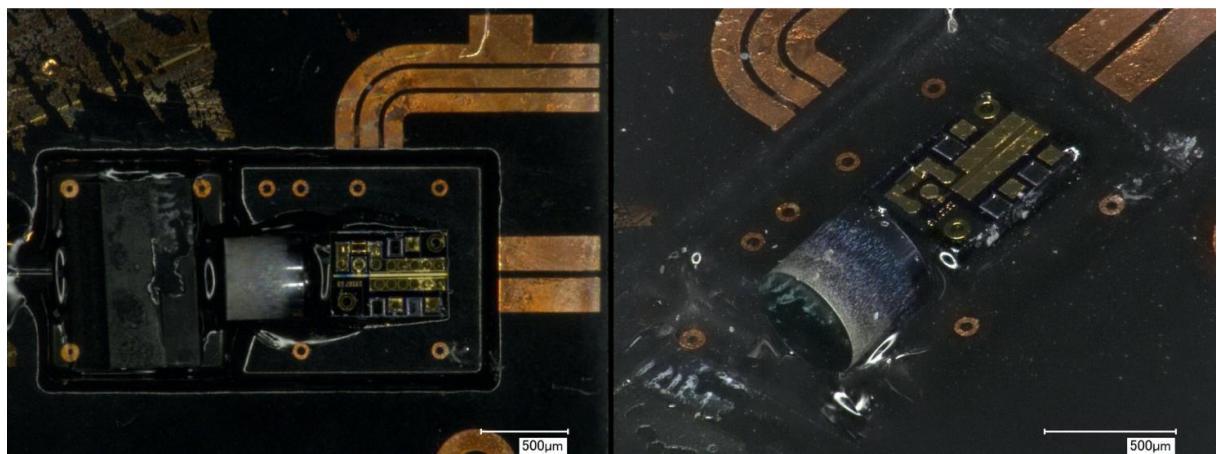

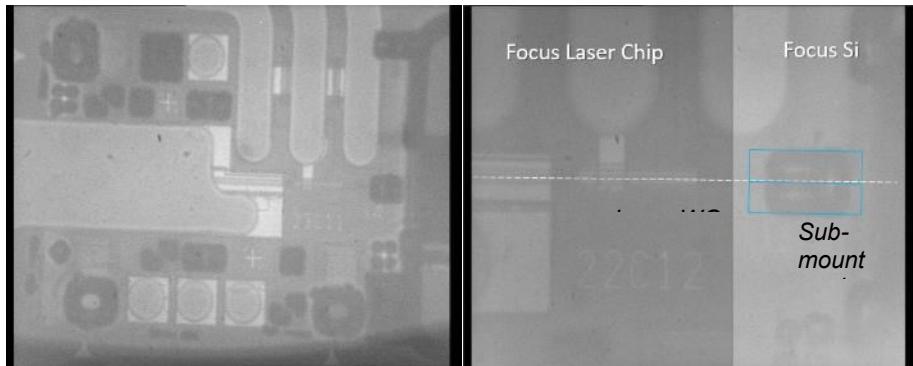

Then, as soon as 3D Si Benchs were available, first FC TC (Flip chip Thermocompression) experiments were started with a precision flip chip bonder on shortloop bumping wafers to evaluate the compression of the bumps with vertical stoppers, as reported in D4.2. Afterward, the process was transferred onto the high precision flip chip bonder, in order to possi-

bly target to the final requirement of submicrometric lateral postbond position. Diverse inspections were performed to check the integrity of the assembled parts, amongst other cross-sectioning (Figure 30).

Figure 30: Thermocompression test with EML v1 to z-stop with gold bumps of 40 µm Diameter (left) and 50 µm diameter (right) (note: cracks are preparation artefact of grinding & polishing)

The cross-sections were further inspected by SEM to examine the bond interface of the gold bump and also the z-stopper (Figure 31). The bump/chip pad interface is still recognizable but the gold bumps seem well bonded in the bump centre.

Figure 31: SEM inspection of the bonded interface at the D50 bump (left) and the vertical stop (right) after flip chip Au thermocompression process (crack in fragile InP probably from grind preparation of cross section)

In regards of inspecting the postbond accuracy, since the EML backside is metallized, the assembly cannot be examined using IR microscopy from the chip side, however through the backside of the silicon (backside of silicon wafer polished for this purpose). But, due to the gold RDL, the entire chip cannot be seen through the submount. For example, Figure 32 / Top-left, one of the z-Stop at corner does depict fracture however related in this particular case to a particle already present prior bonding (red circle on second picture), dirt most probably from InP cleaving, the Chip cleave goes to close to the z-recess and produces particles.

The postbond accuracy can be roughly evaluated by means of the markers present on the chip and submount created in the structuring of the photonic layers (do not work, the markers are not transparent (smooth) enough to see through) as well as by means of the markers and the InP waveguide (Figure 32). The EML seems laterally well aligned with the submount.

Figure 32: Infrared Post bond inspection through silicon submount “fiber only”, top: example with broken InP at one of the three z-stops (sample C07-L08-D40), bottom: example without detected damages (sample C05-L07-D50)

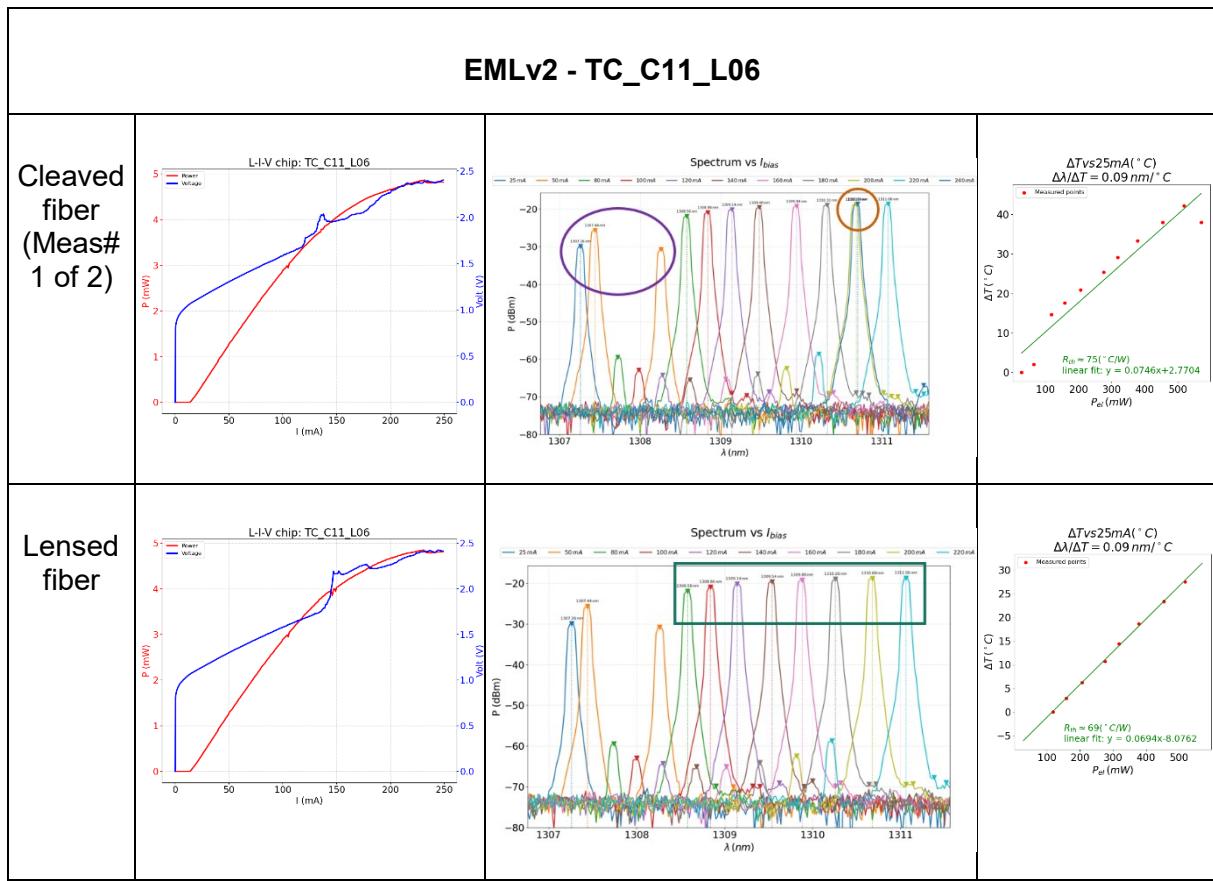

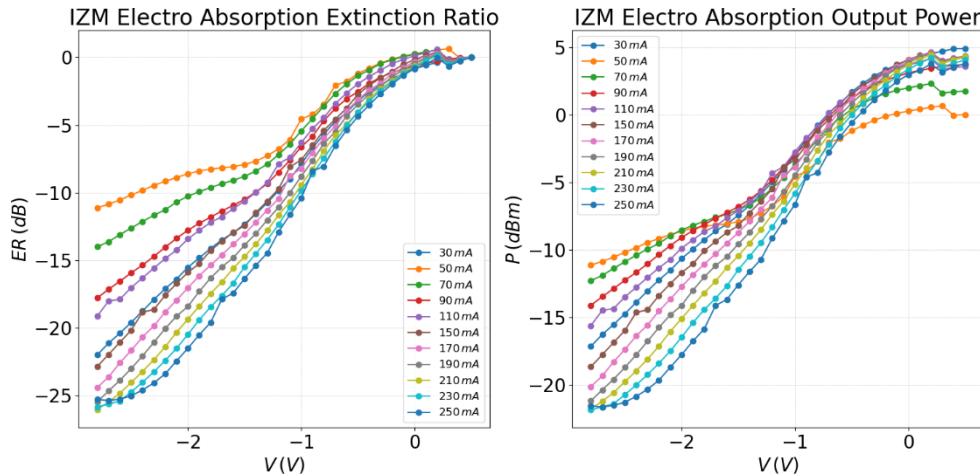

The test vehicles were optically tested by turning on the EML and capturing the light with a cleaved single mode fiber (SMF) placed in the v-groove and approached next to the EML facet. A signal could be detected, coupled into the fiber and a typical LIV curve of the EML measured (Figure 33). On the sample with InP fracture near the z-stoppers, it is not clear, if the unusual LIV curve is caused by the chip as delivered or by the defect observed at the z-stop (Figure 31).

⇒ Nevertheless, this test-vehicle and associated measurement validate the 3D passive alignment.

Figure 33: Tests of “Fiber-only” test vehicles with cleaved SM fiber, EML v1.

## B. Solder Assisted FC Self-Alignment (SA)

First 3D Silicon Benches for FC self-alignment were also fully processed, however the Si-Spike issue led to uncontrollable AuSn bumping process. Consequently, the bumping height, composition and morphology was not compatible with self-alignment due to local bump height variation with FC unconnected bumps and misaligned laser (as reported in D4.2).

Figure 34: Comparison of Bump height inspection, as plated (left) and as reflowed (same, filtered to upper part), X-Ray and Backside Infrared inspection after SA flip chip

Several bumping rounds on 3D SiBench wafers were necessary and performed to cope with this aspect, leading to further postponements. A final 3D Si wafer could be finalised Mid-August 2022 and provided for first tentative of FC Self-alignment.

Several iterations of FC Self-alignment were performed on parts of the wafer, with some positive results as revealed by cross-sectioning onto 3D stoppers (Figure 35). Further experiments should be performed, with wafers of second generation, out of the project timeframe due to accumulation of technical issues, resource overload and overall delays (partly, COVID-19 causes and consequences).

The EU Report/Deliverable D4.2 – High precision photonic packaging - gives further insight on the work performed.

Figure 35: Flip chip Self alignment results @ M42 (Cross-sections)

## Task 4.3 Bonding technologies for sensitive optical components

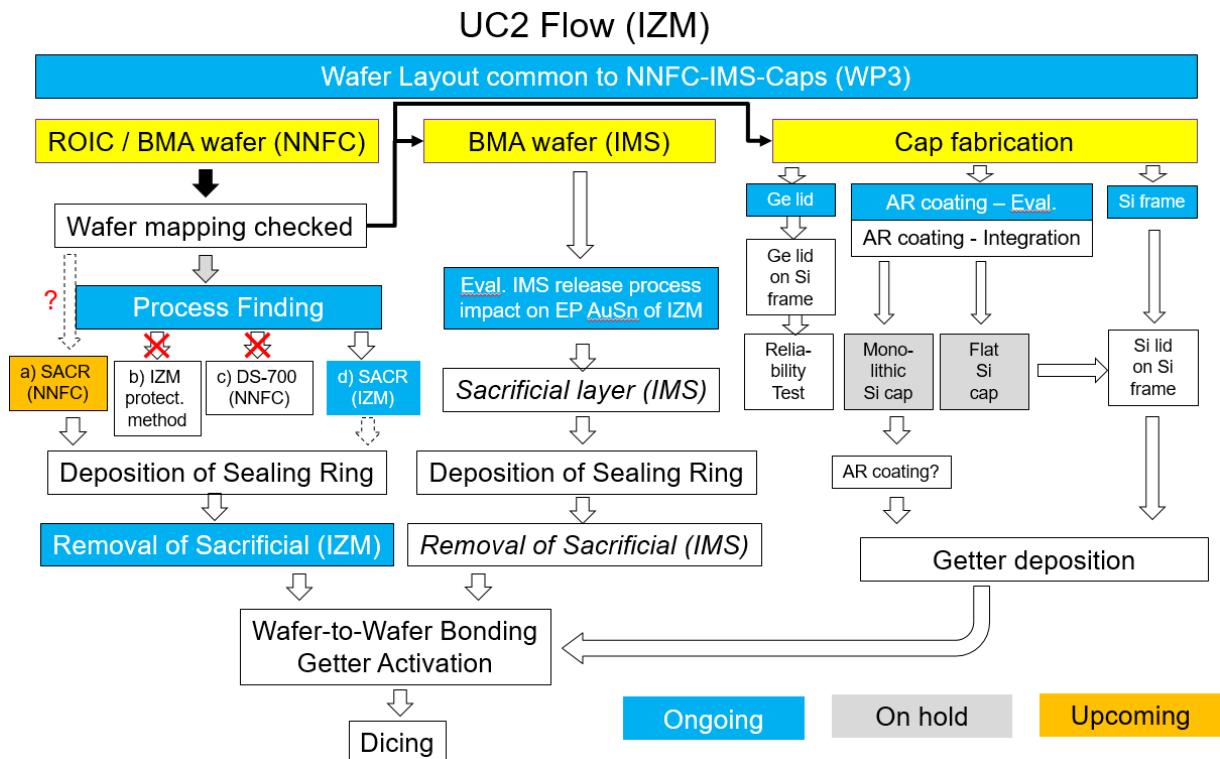

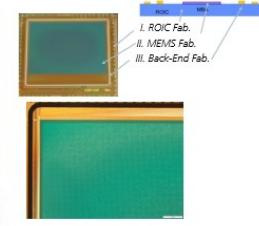

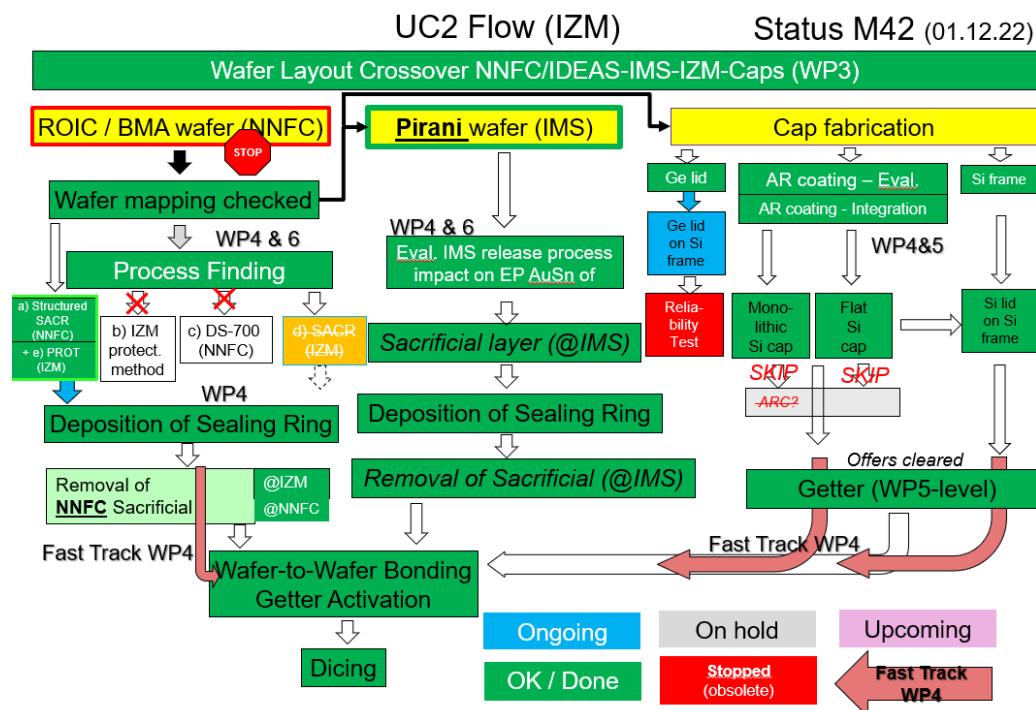

In this task 4.3, wafers were processed in view of preparing WP5 / hermetical sealing of fully functional microbolometers. Figure 36 gives an overview of the general workplan.

Figure 36: General Flow Diagram UC2 (IZM @ M20 / End 2020)

The Figure 37 below recapitulates the retained packages topologies and the corresponding parts needed for performing the corresponding wafer level packaging, each wafer type being labelled by a letter (A to E).

Figure 37: Three WL package topologies

WP4 grade bolometers are test wafers, WP5 grade relates to functional parts (Bolometers MEMS under fabrication at IDEAS/NNFC and FhG-IMS). Capping parts for WP5 enclose additional features, an ARC (Anti-reflection Coating) and getter, and are fabricated in high IR-transparent Silicon grade.

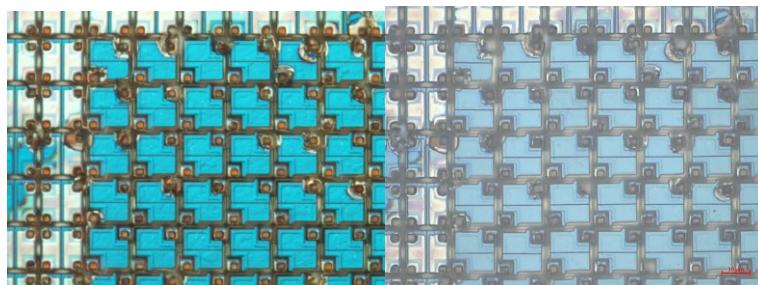

#### 4.3.1 a) Sensor-Wafer preparation

Metallic sealing is targeted for hermetical bonding of the cap window onto the bolometer device. Different process flows have been drafted depending on the four cap topologies considered. The main bonding technology being considered for the wafer level capping of the bolometer structures on ROIC wafer is Transient liquid phase bonding (TLPB) with gold-tin (AuSn)

metallurgy. This relies on the formation of an AuSn20 eutectic (i.e. a molten “phase”) being transformed into a single higher remelting metallurgical Au<sub>5</sub>Sn phase so that the sealing rings do not remelt during typical solder SAC reflow, which should permit next level integration without deteriorating the sealing of the package, a.o. due to thermal budget in subsequent integration levels (no remelt of the sealing join). Thermocompression bonding was also optionally considered at project begin to seal the cap with the ROIC device using gold rings instead of AuSn solder-based rings, but had to be withdrawn to limit the work load vs. COVID-19 situations.

Following major processes are required for the preparation of the Sensor Wafer:

1. Local structuring (opening) of release layer (supported by means of lithography structuring and plasma etching)

2. Electroplating Deposition of sealing ring structures (Gold or Gold-tin, still to be defined) in semi-additive process, supported by means of Sputtering (adhesion/barrier/seed layers) and lithography processes and etch removal of sputtering layers,

3. Electroplating / Deposition of stoppers in a similar manner, supported by means of lithography processes,

4. Entire Release of Microbolometer MEMS Structures

5. Annealing for degassing

6. Wafer bonding with capping counterparts

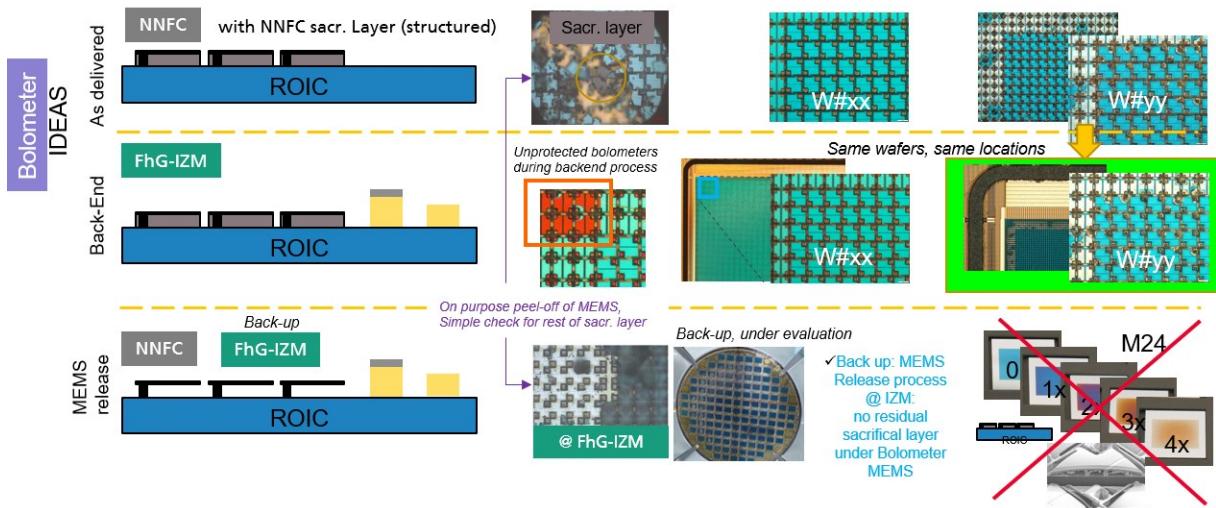

Compatibility of the MEMS release layer is a key point for back-end processing. This release (also called sacrificial) layer, processed by bolometer supplier/fabricant, not only permits to fabricate the MEMS membranes forming the bolometers, but also protects them by bringing mechanical support or even embed them for protection of their upper surface. This item is a predominant/impacting aspect, which determines the most adequate process flow for correct wafer preparation, not only for the sensor itself but also the different capping counterparts to be bonded on. Especially regarding compatibility with back-end wafer level processes in place at Fraunhofer IZM (for example, compatibility versus resist processing for photolithography processing).

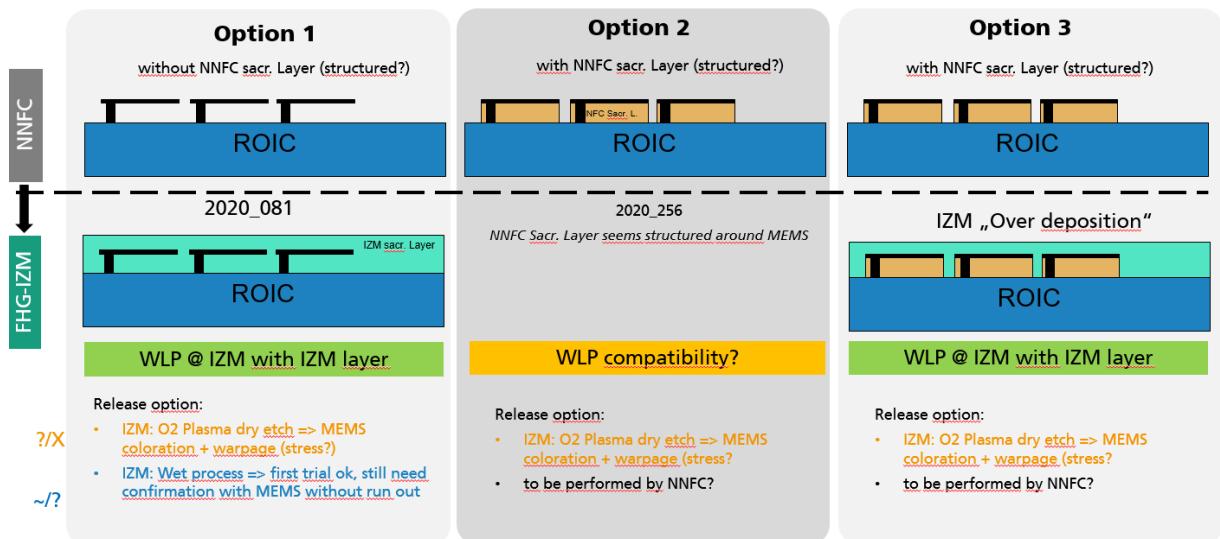

Effectively, in order to carry out back-end, the thin bolometer MEMS membranes must be constantly protected over all the different process steps and the release of the layer must be compatible with the performed back-end preparation. However, during 2020, it figured out that the MEMS Fabricant of IDEAS (NNFC in South Korea) withdrew its sacrificial material and could not anymore deliver bolometers with the first-expected sacrificial layer, due to process stop at their fabrication site.

Apart of this, extensive basic trials were also necessary to even find a way to proceed with this unknown / external material composing the release layer.

Three options were identified as illustrated in Figure 38:

1. The first one relies on a proposition of IZM to apply a sacrificial release layer by their own, since the original sacrificial layer cannot be anymore provided by the MEMS fabricant. This means that the MEMS are delivered fully unprotected and that Fraunhofer IZM must develop a new process to sustain (“underfill-like”) and protect the very thin MEMS membranes, without damage, collapse nor bend of the membranes, with a 2 µm gap between MEMS plates and ROIC.

2. The second one foresees, the original sacrificial layer is back at the MEMS fabricant and is compatible to all processes at Fraunhofer IZM, including wet processes (lack spin, lack removal, and related solvents as well as plating bath), without mechanically

damaging nor chemically damaging the exposed MEMS membranes as well as the sacrificial layer itself. This is very unsure, since the sacrificial layer is a non-identified / unknown external material at Fraunhofer IZM (not in process program)

3. The third relies on the applying an overdeposition with a material of IZM, embedding the MEMS, themselves sustain by a sacrificial layer provided by the MEMS Fabricant/provider.

All the three options also imply that the removal of sacrificial and/or protective layer does not affect the MEMS. Most naturally and preferred version would be the use of the original sacrificial layer, since the fabricant must know how it behaves/impacts in respect of the MEMS functionality, nevertheless its compatibility could not be fully assessed within the IZM process flow.

### APPLAUSE UC2, NNFC bolometer

Figure 38: Interfacing delicate Bolometer MEMS with Wafer Level Packaging

The option 1 and 3 were then retained and tested, not only for applying the over-protective layer but also to remove it safely.

In option 1, process finding regarding applying and removal of a sacrificial/protective layer prepared by IZM were performed with NNFC shortloop wafer delivered by IDEAS with free-standing / unprotected bolometers. Here IZM tried to apply a layer “embedding” the thin MEMS membranes, to 1) mechanically sustain the thin membranes having a 2µm gap to substrate and 2) to protect the bolometer MEMS top surface during processing of the bolometer wafers at IZM. The results were at first sight positive, however, all results were jeopardized, since it appeared in retrospect that the provided wafer material was partly defective, with MEMS membranes already stuck down or even crashed. A precise statement on the performed processes with Fraunhofer ZM material for sacrificial layer, if affecting the tiny MEMS-Membranes (up or stuck down), could not be done (Figure 39). A methodology of precise inspection of specific MEMS membranes was took in place afterward to leverage this point for further works.

Figure 39: Short loop Bolometer Wafer of NNFC/IDEAS with sacrificial layer applied by Fraunhofer IZM. Some MEMS are stuck down.

Since the original sacrificial layer applied by the bolometer manufacturer NNFC was again available (Oct. 20), a second track was reopened with option 3, starting with wafers with the original sacrificial layer as originally planned (NNFC sacrificial layer) and only under the MEMS, with surrounding free of it for fabrication/electrodeposition of metallic bond rings. The purpose was 1) the testing of feasibility of removal tests at IZM and 2) to evaluate if those wafers are compatible with wafer level processes of IZM, especially lithography and the deposition of the bondrings by electroplating.

The results of all the different tests revealed that option#3 was the most promising (less-risky) for handing over IDEAS/NNFC bolometer wafers to IZM for wafer level processing and packaging of the MEMS-based sensor. A process method has been here found to keep the MEMS membranes safe over the Back-End processing at FhG-IZM.

Those assessed process developments should have been used for post-processing of functional bolometers within WP5. Nevertheless, functional wafers (WP5) could not be provided by IDEAS to FhG-IZM, due to low yield in MEMS fabrication by IDEAS subcontractor NNFC. Test wafers with bolometer MEMS from IDEAS/NNFC have been processed, results are reported below in WP5 / T5.2.2 Microbolometer preparation.

Test Wafers from FhG-IMS with only IMS sacrificial layer material (“IMS\_s”) and dummy MEMS (“IMS-MEMS-Dummy”) have been also processed for interface/ process compatibility testing. The IMS sacrificial layer and its release was compatible with the wafer process of FhG-IZM.

Wafer bond were performed with all those base wafers with cap wafers.

#### 4.3.1 b) Silicon Frame Wafer

The silicon frame wafer is an intermediate part between the ROIC/MBA wafer to bond the flat germanium window. It permits to create and adapt an internal volume for vacuum sealing which else would be too small by bonding directly the flat lid/window onto the microbolometer. Germanium and silicon lids were similarly bonded on the silicon frame and then compared in terms of characterisation/failure (WP6).

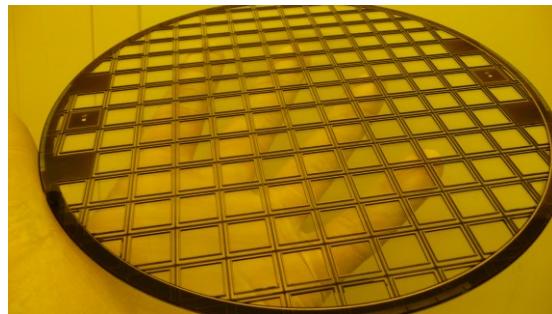

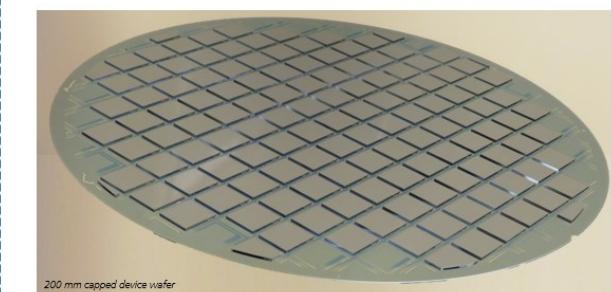

The fabrication of the silicon frame on 200 mm wafer (Figure 40) consists in general onto electrodeposition of the bond rings on both sides and etching through the silicon over the place where the pixel matrix of the MBA is.

### C. Si Frame

Var. Small Lid

Result of processing

Figure 40: Silicon frame wafer with through DRIE etched cavity

Fraunhofer IZM fabricated silicon frame wafers by silicon dry etching (Figure 41). The Silicon Frame includes gold bond rings on its both sides (Front and backside) for joining with AuSn bond rings (processed on Silid and Base/device wafers). Those Si-Frame wafers were first bonded to silicon lids and then to base/device wafers.

Figure 41: Fabricated Silicon Frame wafer, 200 mm, prior wafer bonding with Si Lid

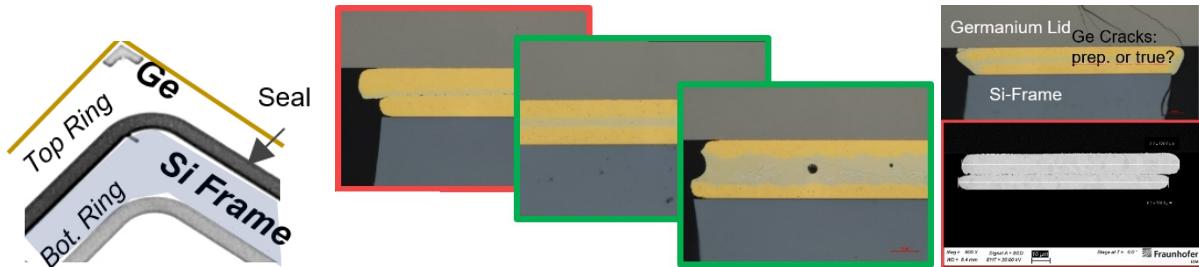

#### 4.3.1 c) Reconfiguration of Germanium Windows (and Silicon Lids)

- Germanium lids

After discussions with UC2 leader IDEAS, silicon capping has been considered as more straight forward regarding the system and packaging. Germanium remains a candidate but as explorative work due to heavy concerns on high CTE mismatch with silicon.

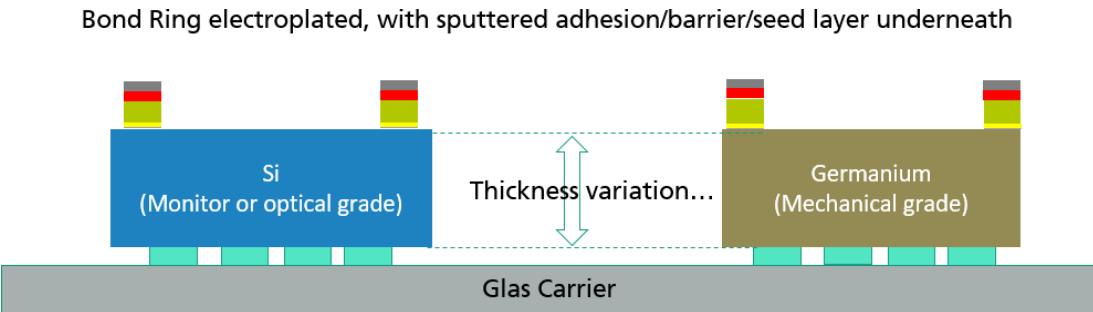

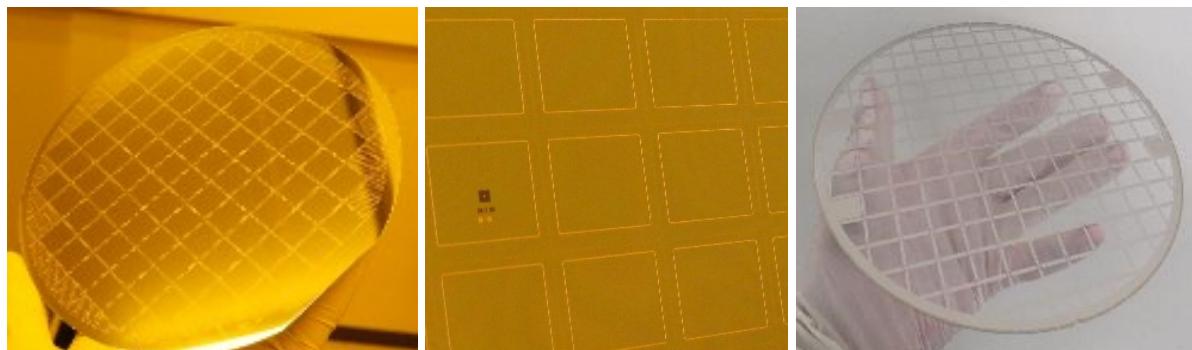

Despite of the concerns, Germanium wafer in technical/mechanical grade were purchased for evaluation purposes. A process flow was drafted for preparation of seal bond rings, dicing and reconfiguration of Si and Ge Windows chips on a temporary carrier.

Figure 42: reconfigured Silicon and Germanium windows

Processing of the reconfigured Ge and Si windows (Figure 42) consists mainly in electro-deposition of Au (or AuSn) bond rings for sealing on Ge and Si wafers, Stoppers for wafer bonding, dicing of the wafer, reconfiguration of singulated parts on temporary wafer for wafer-to-wafer bonding onto Si-Frame wafer and then onto ROIC/MBA Wafer.

- Die level lid (germanium) (label E, fig. 12)

Ge Lids were prepared with AuSn bond ring from 6'/150mm Ge wafers for bonding to 8'/200mm Si-Frame Wafer. Due to wafer size (and CTE mismatch to Silicon), the Ge Wafers have to be diced in single lids, then to be reconfigured on carrier to adapt the wafer size and grid.

For this, dedicated 200mm temporary carriers have been fabricated at Fraunhofer IZM (Figure 43) for the reconfiguration of single lids and subsequent wafer level bonding and clean carrier debonding.

Figure 43: Left & Center - Germanium wafer (150 mm, 230  $\mu$ m thick) processed as Lids prior singulation; right : special 200 mm carrier for wafer cap processing and reconfiguration of lids and wafer level bonding, 200 mm wafer.

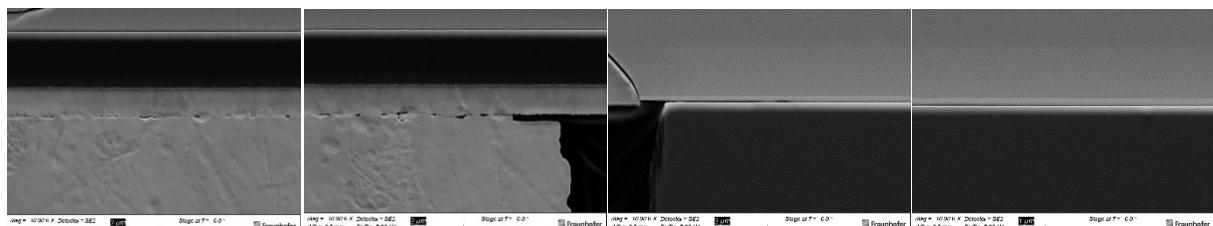

Die level reflow and chip bonding tests (Figure 44) were performed using AuSn bond ring on Germanium (mechanical grade, three wafers) and silicon frames as bond substrates (having failed at through cavity silicon etching). The AuSn reflow depicted correct composition (ie. enough eutectic part) on only one of the three germanium wafer with rounding of the solder (Figure 44, center left), the two other wafers presenting fully insufficient melting behavior or insufficient total height. After chip bonding, due to overlapping of Au-based rings on the Si-frame top and bottom side (from layout), the sealing quality can only be partly inspected by X-Ray microscopy in tilted angle (part of WP6). An example is given in Figure 45/left.

Figure 44: Package topology Germanium on Si frame in (E: Ge Lid, S: Si-frame, A: bolometer), re-flowed AuSn Ring on Germanium lid, and die level bonded germanium lids on Si-frame with cross-section.

Figure 45: Left: X-ray inspection of single Ge-lid bonded with AuSn ring on Si-Frame in tilted view, Center: cross sectioning of sealed ring of three germanium lids of 3 different Ge Wafers, Right: Cross-section with crack in Ge (top), SEM of AuSn seal with insufficient solder amount (bottom).

Many cracks are visible in cross-section in Silicon or/and Germanium as well from top view on Germanium after Die Level Bonding, most probably due to the large chip size (~11x12 mm) combined to the difference in thermal expansion (CTE Mismatch) resulting in a very high level of mechanical stresses (as also evaluated by thermo mechanical simulations, not shown, FhG-ENAS). It leads to the conclusion that large Germanium chips are not suitable for bonding onto Silicon with AuSn. Due to these pre-results, the focus was displaced to Silicon Lids instead of Germanium lids as a countermeasure.

After official project end, remaining most adequate (in respect of deposited Au/Sn layers) Ge-Lids were reconfigured on carrier and bonded to remaining Si-Frame wafer (Figure 46, left)

Figure 46: Reconfigurated (1:4) Carrier with single Ge-Lids (left) and cracks in Ge-Lids after AuSn Wafer bonding to Si-Frame Wafer

Apart from some post bond misalignment between Lid and Siframe, the Germanium parts were all presenting fractures and cracks ((Figure 46, right), similarly to the chip level trials. This result definitively rejects the feasibility of bonding large Ge chips to Silicon substrates using AuSn bonding and peripheral rings.

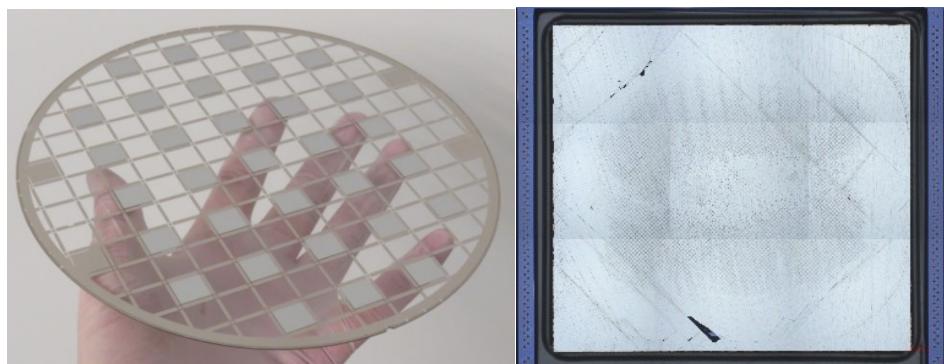

- Silicon lids & silicon monolithic cap

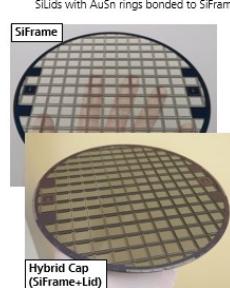

Wafer for Silicon lids (to be bonded with Si-Frames) were prepared for AuSn wafer bonding, inclusive integration of getter material (subcontracted to SAES).

Singulated SiLids were also reconfigured (Figure 47), prior joining to Si-Frame.

Figure 47: SiLids reconfiguration (picture left, single lids originating from two different SiLids wafers)

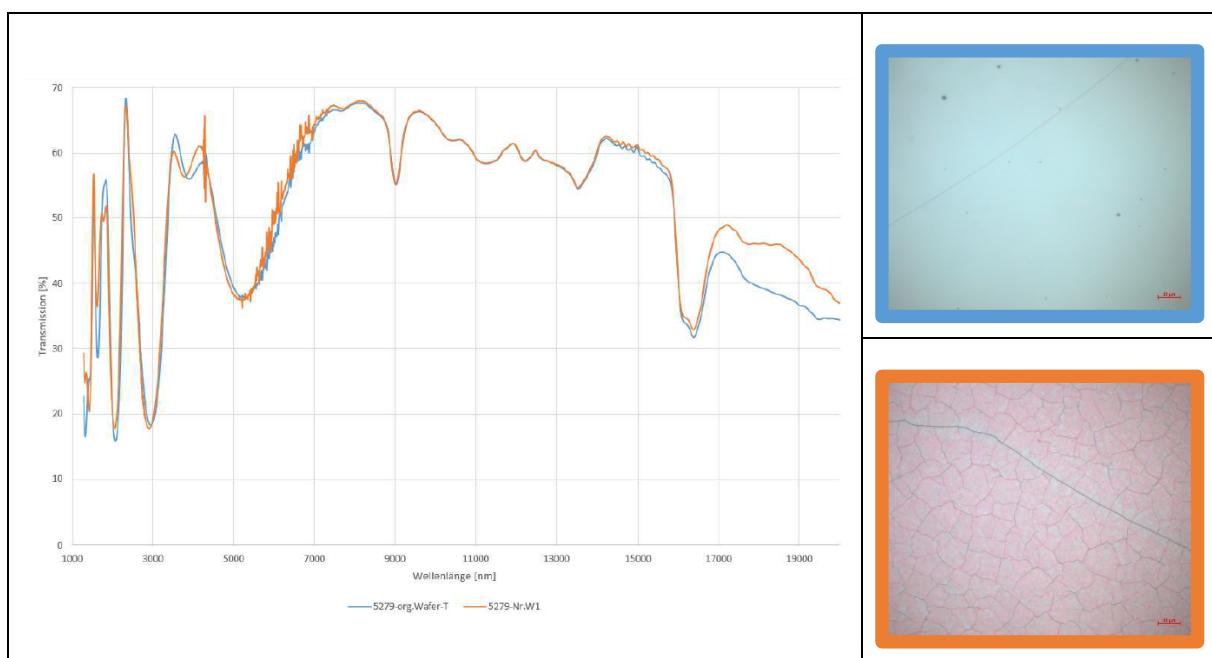

- Silicon monolithic cap.

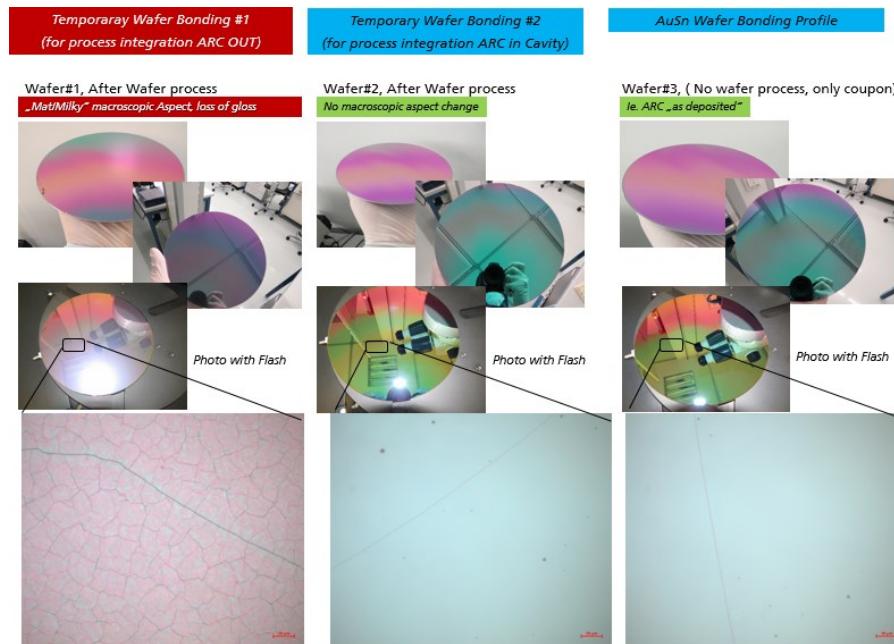

For the purpose of UC2, European providers of optical grade silicon wafers for the silicon cap material (ie. compatible for IR applications, low absorption around 9 $\mu$ m) as well as anti-reflection coating for silicon substrate have been identified and contacted. Depending on their capabilities (Si optical grade in 200 mm with AR coating, double or single sided) and the interactions with the envisioned process flows for the cap fabrication and sealing at IZM, it will further steer and determine the cap process flow and related topology to be implemented.

A monolithic silicon cap wafer (Figure 48) is in between also considered, which will comprise the Anti-Reflective Coating (ARC) on its outer side, electrodeposition of the Au sealing bond ring, Stoppers, etching of cavity by DRIE, deposition of ARC inside the cavity, getter deposition, pre-dicing, and finally wafer bonding to ROIC/MBA Wafer.

Figure 48: Concept of monolithic silicon-based cap

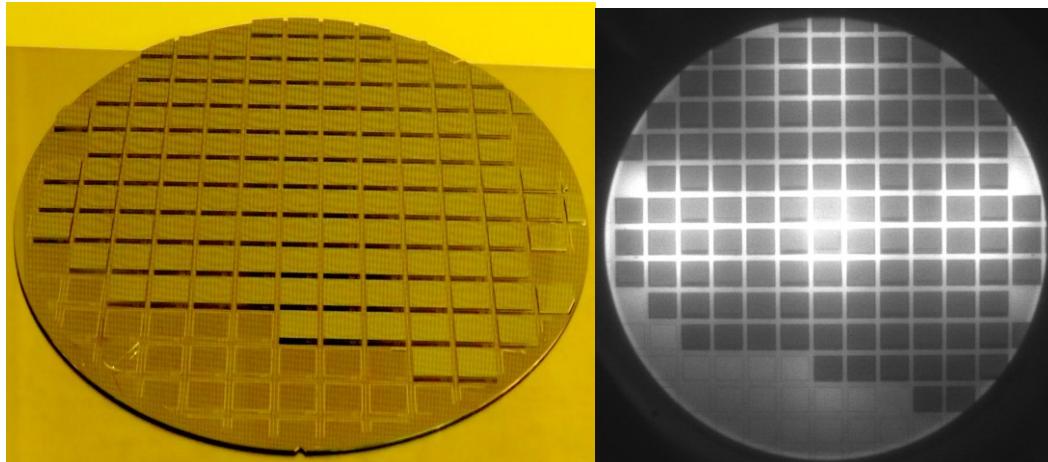

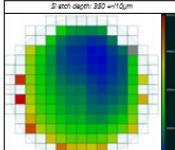

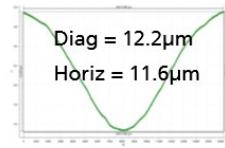

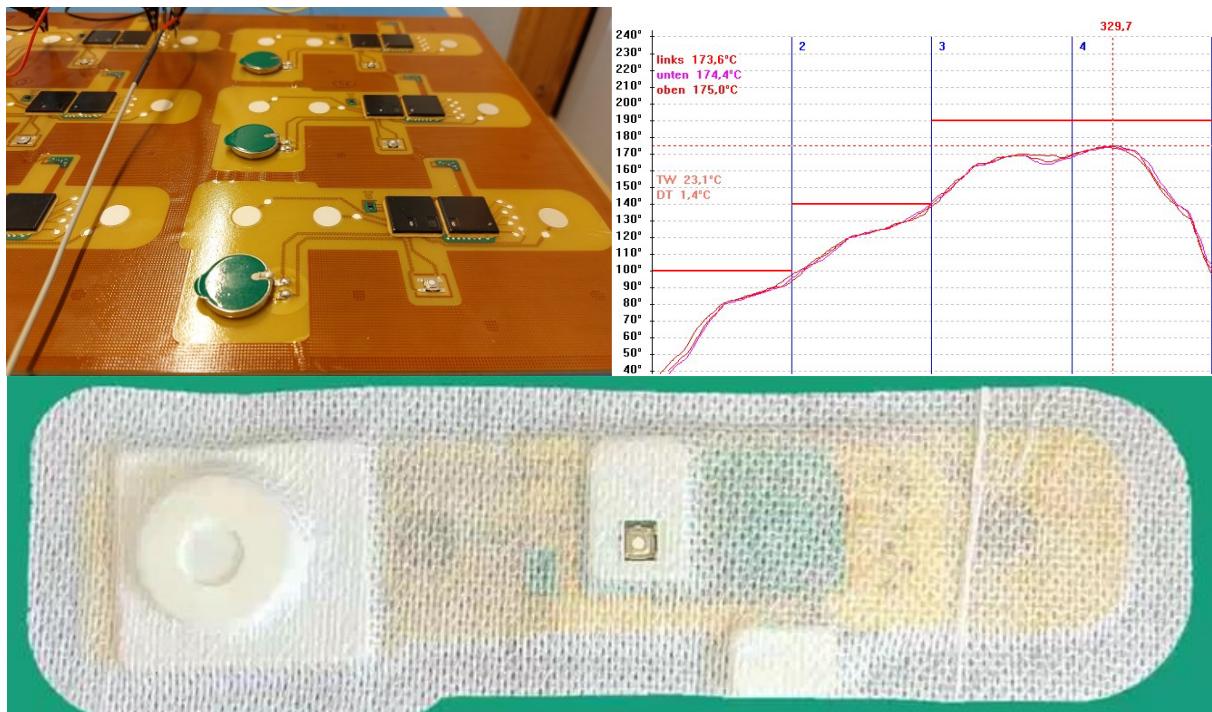

Silicon wafers for monolithic cap were fabricated (Figure 49) by means of lithography technics combined with additive (electrodeposition of metal rings) and subtractive processes (Si plasma etching Bosch Process, wet etching of metal layers), inclusive trials to improve the etching quality of the deep cavities over the 200 mm wafer (tuning of etch depth to reduce the dispersion/deviation over the wafer around +/-10  $\mu$ m, activity WP5-level).

Figure 49: Silicon monolithic cap wafer, with  $350\text{ }\mu\text{m}$  cavities and getters, before bonding to device wafer.

#### 4.3.1 d) Bonding of 3-Stacked Wafers

After the individual preparation of the packaging parts, wafer bonding was performed to stack and seal the different parts together. In the case of the monolithic Silicon cap, the gold bond rings were sealed with the AuSn ring on the bolometer under vacuum chamber into the wafer bonder (Figure 50).

Figure 50: Monolithic Silicon cap bonded on ROIC/MBA wafer

In the case of the silicon frame, two bond sequences are at this stage under consideration, where the reconfigured windows are first bonded with the silicon frame, this stack being then bonded further on onto the ROIC/MBA wafer, or the other way around, with first the silicon frame bonded onto the ROIC/MBA and then capping with the reconfigured window (Figure 51).

## C. Si Frame

Var. Small Lid

Result of processing

Figure 51: Stack of ROIC/MBA wafer, silicon frame and reconfigured Windows (silicon or Ge)

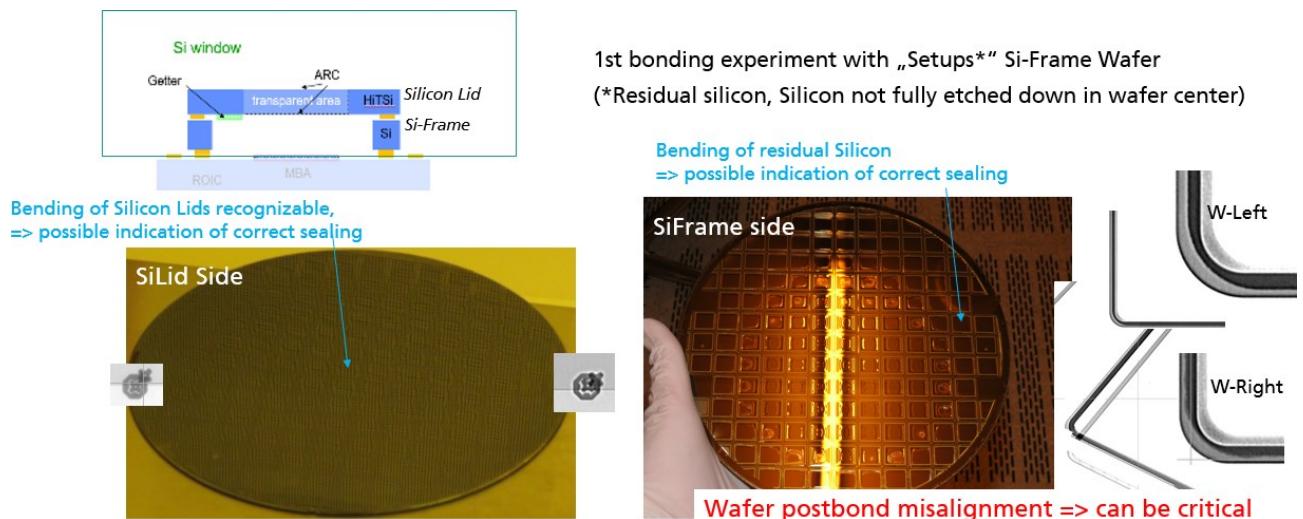

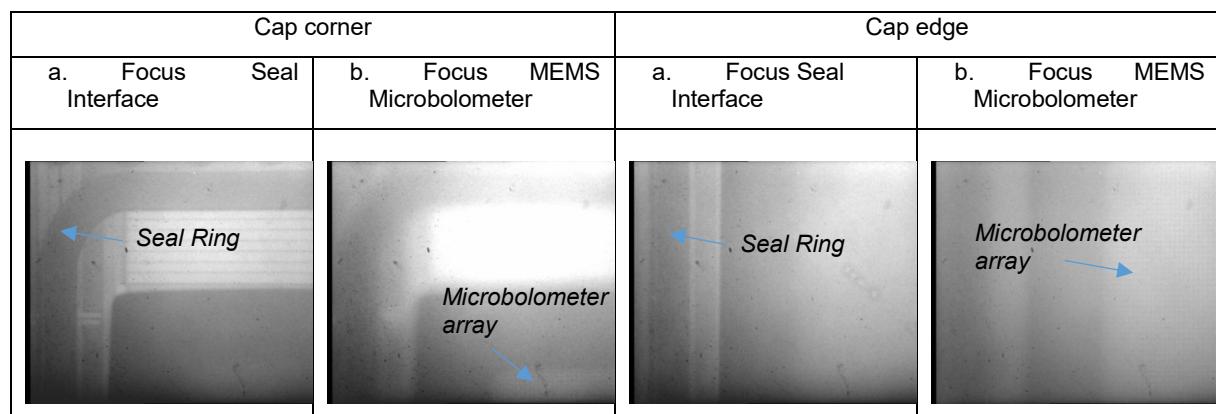

The first W2W bonding attempt (Frame to Lid) was not promising but permits to identify few blocking points (Figure 52). The poor post bond misalignment leads to narrow bond line at the corners of the bond ring. None the less, the visual observation of both wafer outer sides reveals some silicon bending (deflection on Si lid side and on residual silicon membrane in the frame), sign of a possible seal. The wafer stack was not further investigated, since of low value.

Figure 52: First Trial of W2W Bonding of Si-Lids and Si-Frame

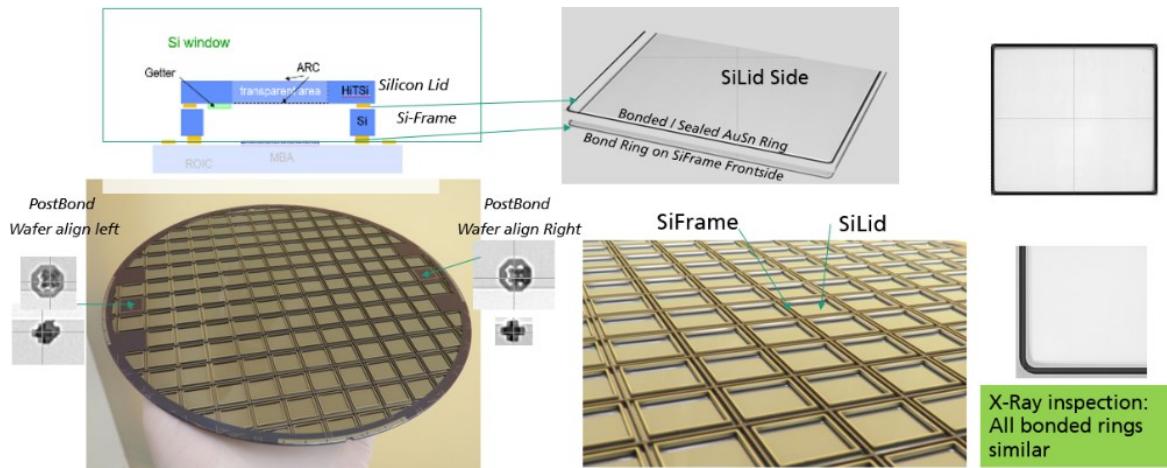

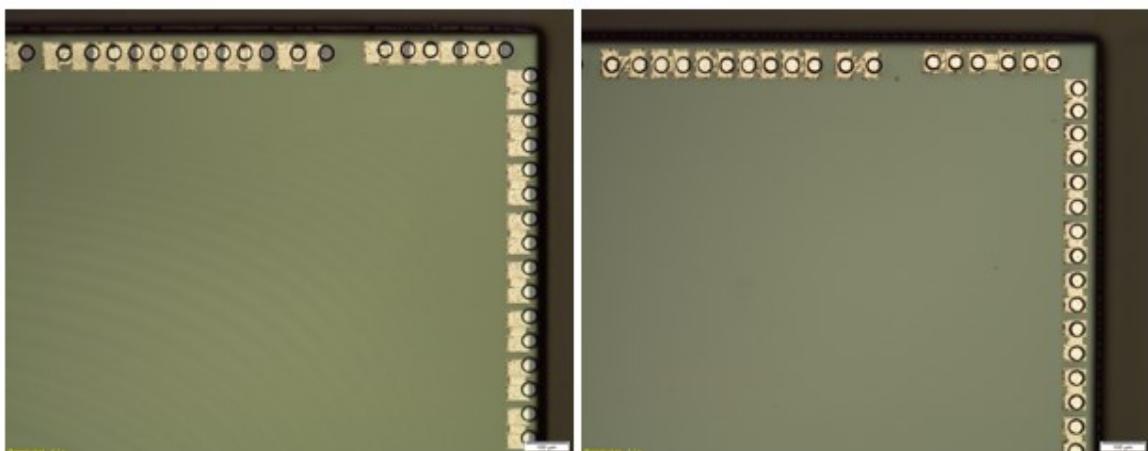

The bonding process was then improved, especially the pre-bond preparation of the Silicon-Frame and the alignment procedure (Figure 53). The post bond X-Ray inspection of the wafer stack is satisfying, both wafers are still correctly aligned and the rings seem all to be bonded, the ring corners do not display particular risk of leakage, and even the bonded rings seem to have less voids than in the other wafer bond. No destructive physical analysis has been performed, the Si-Window will be first bonded to a bolometer/sensor wafer (test or functional).

Figure 53: Fabricated Silicon Window with improved W2W AuSn bonding process (HybridCap#02)

Having achieved the first “stage”, the silicon window wafers (also called hybrid cap, consisting of SiFrame bonded to Si Lid Wafer) were bonded on the base/device wafers.

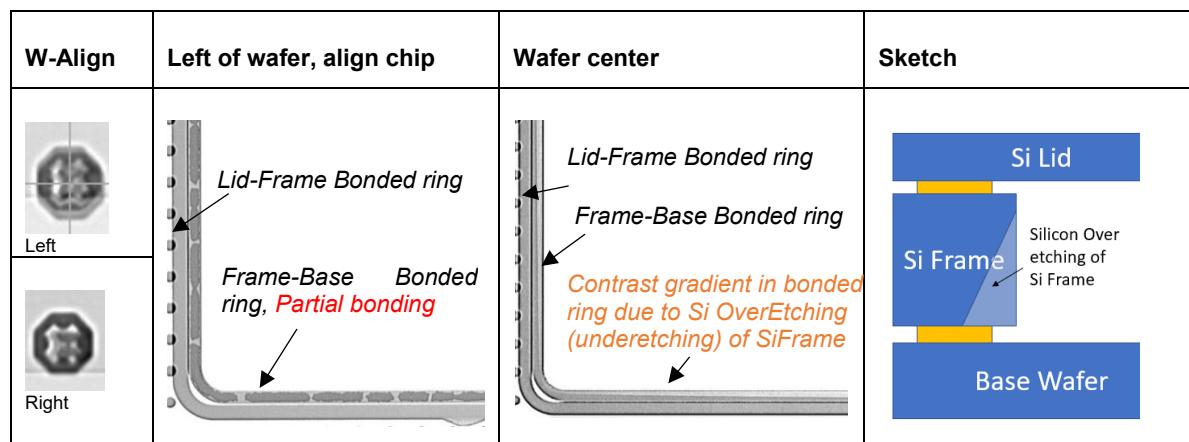

The results were partly satisfying: the first bond test to a base wafer (with the hybrid cap of Figure 53) was encouraging: despite some unbonded ring areas (Figure 54, left) and silicon over etching of the Si Frame backside (Figure 54, right), the bond rings to the base wafer were generally sealed.

Figure 54: X-Ray inspection (example) after bonding of HybridCap#02 on base wafer. Picture Left: ChipAlign Left & Picture Right: Wafer center

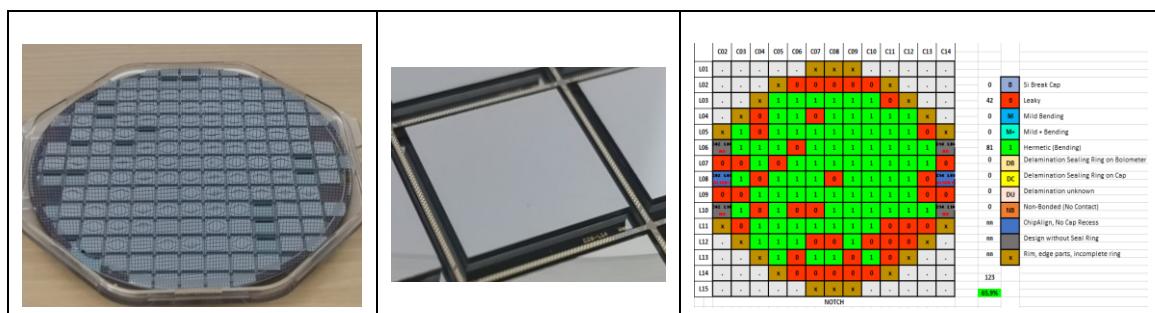

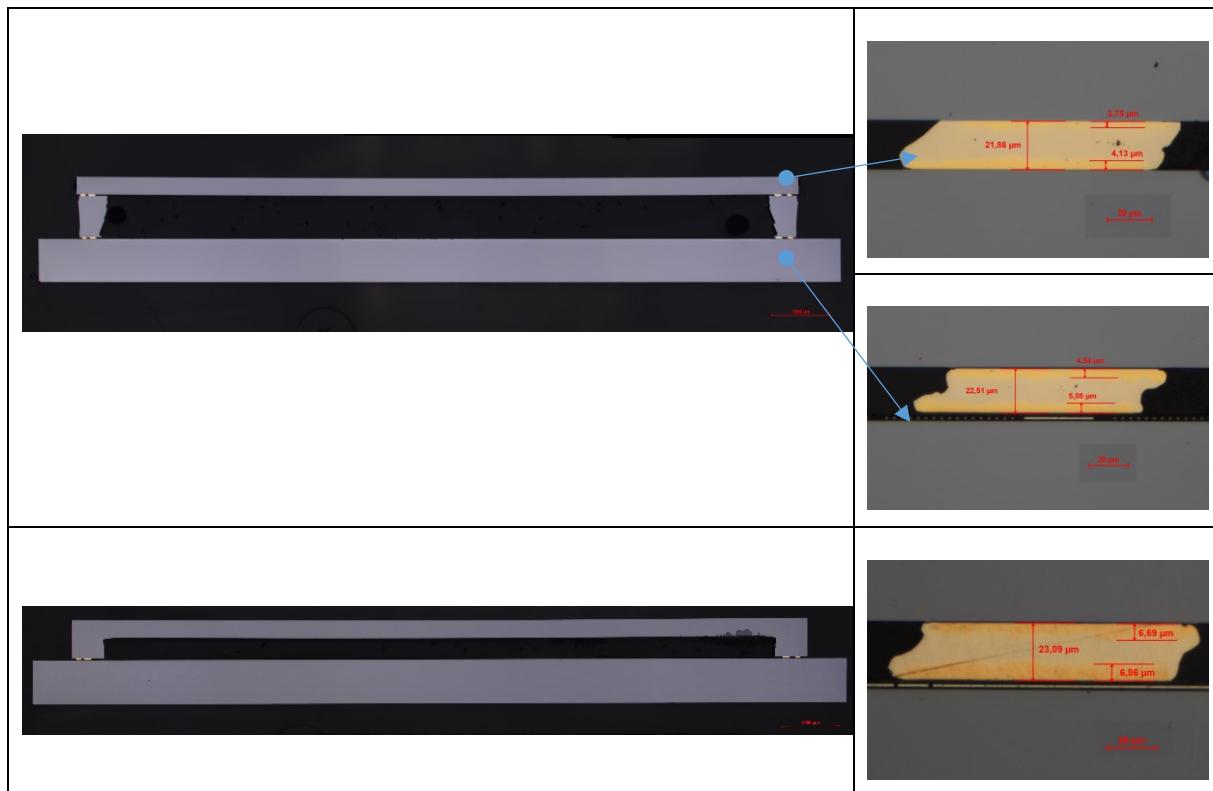

After removal of Si Lid Carrier, 81 of 123 devices were still sealed after “double AuSn bond” (Figure 55), i.e. ~66% sealing yield (based on silicon lid deflection).

Figure 55: HybridCap#02 bonded to device wafer, after 1 year ambient storage

However the other bonded hybrid cap (#03,#04,#05) revealed some misalignment and/or incompletely sealed rings to the device side, already during bonding between Lid and frame. The bonding to Pirani MEMS wafer (base/device wafer) was then unsatisfactory.

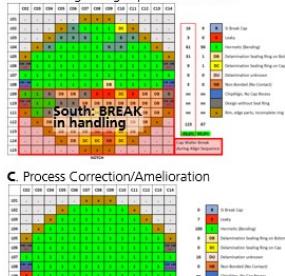

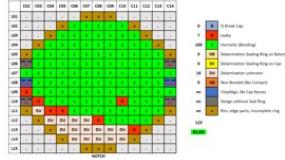

Wafer bond trials with cap wafer (see below and task 5.2.3) leaded in general fortunately to better bond results (Figure 56), i.e. higher yield up to 80% in WP4, since only one wafer bond is involved for wafer sealing.

Figure 56: Macro-inspection after Wafer bonding and Carrier release of monolithic cap: silicon deflection (left) and IR-Photography (right)

#### T4.3 - Summary

Wafer level bonding with AuSn technology was performed:

- to bond (seal) base device wafers with monolithic cap wafers, for bonding setups

- to seal SiLids with SiFrames, creating hybrid cap wafer

- and then sealing the hybrid cap to base wafer

inclusive dicing of cap wafer and base wafer. Figure 57 recapitulates the WP4 works and main results. Bond results were evaluated by X-ray inspection and yield estimation performed by observation of Silicon bending on cap side. A yield over 80% could be reached in process setups, inclusive cap and base wafer dicing.

The reason for yield “loss” is in between also identified and mostly related to handling of cap wafer and some adhesion issue of the electrodeposited bond rings to the bulk silicon.

The different sealing WP4-level trials fulfilled entirely their aim with support for WP5, for successful sealing results in WP5.

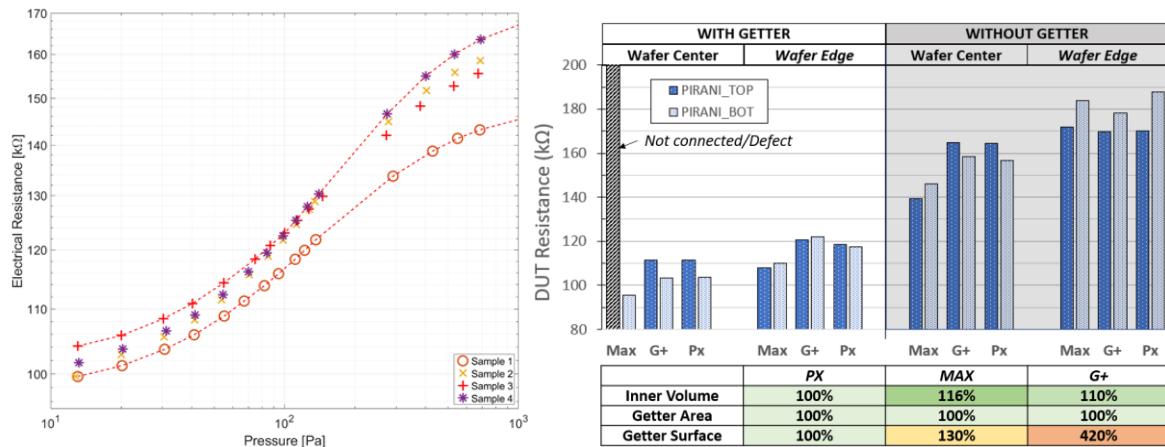

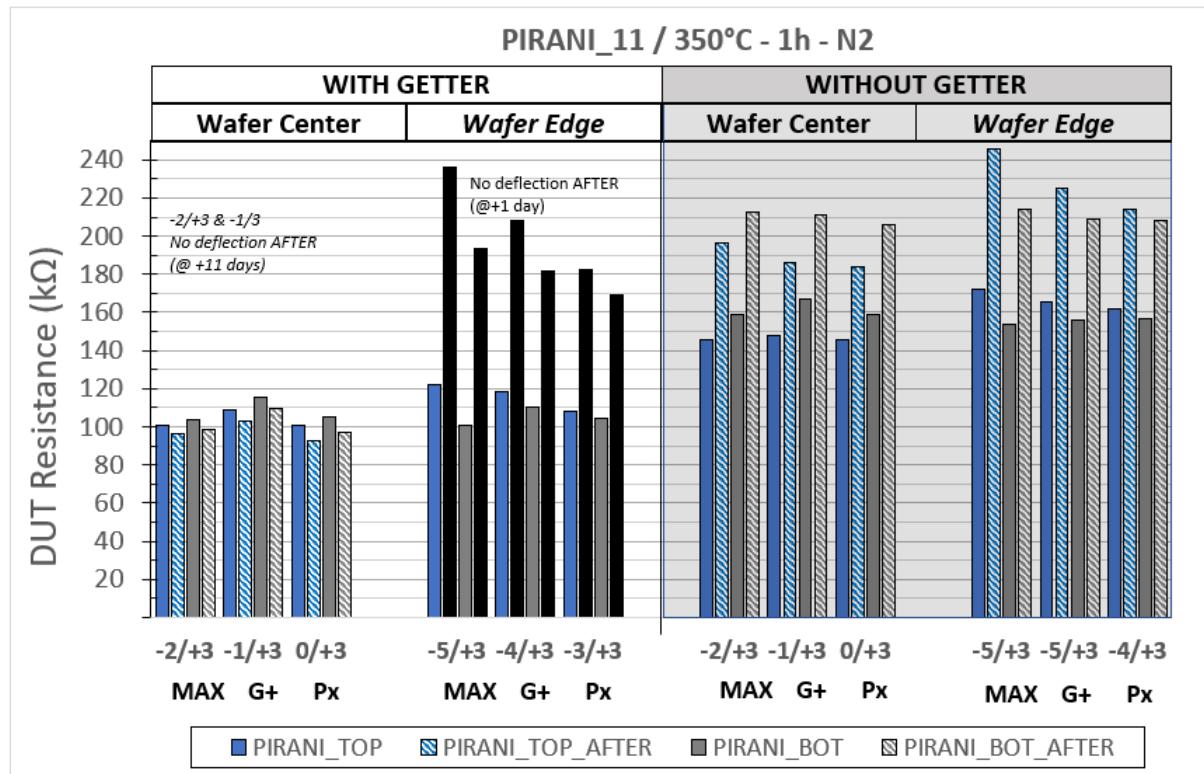

In the frame of WP5, functional Pirani MEMS wafers from IMS were sealed for evaluation of residual pressure (vacuum level/quality) inside the WL packaged devices (collaboration work with IMS and USN, paper presented at ECTC2023).

The EU Report/Deliverable D4.3 - Bonding Processes - gives further insight on the work performed.

## Wafer Level Packaging for thermal imaging MEMS-based sensors

In collaboration with: **ideas**

### I. Background / Goal

#### Wafer Level Packaging for large MEMS array IR Sensors

##### • Silicon Cap fabrication, incl. :