## Abschlussbericht 2023

### Forschungsvorhaben des BMBF

**Verbundvorhaben: PEARLS- Photonic Embedding of Active Region LASER Chips on Silicon**

**Teilvorhaben: Si & III-V Waferprozessierung und Bonding**

**Akronym: PEARLS**

**Projektleiter:** Piotr Mackowiak

Fraunhofer IZM

Gustav-Meyer-Allee 25

Telefon: +49 30 464 03 7981

Fax: +49 30 464 03 128

Email: [piotr.mackowiak@izm.fraunhofer.de](mailto:piotr.mackowiak@izm.fraunhofer.de)

**Inhalt**

|                                                                                           |          |

|-------------------------------------------------------------------------------------------|----------|

| <b>ANGABEN ZU DEM ZUWENDUNGSEMPFÄNGER.....</b>                                            | <b>3</b> |

| <b>1. KURZDARSTELLUNG.....</b>                                                            | <b>3</b> |

| 1.1. Aufgabenstellung .....                                                               | 3        |

| 1.2. Voraussetzungen.....                                                                 | 3        |

| 1.3. Planung und Ablauf des Vorhabens.....                                                | 3        |

| 1.4. Wissenschaftlicher und technischer Stand .....                                       | 4        |

| 1.5. Zusammenarbeit mit anderen Stellen.....                                              | 5        |

| <b>2. EINGEHENDE DARSTELLUNG.....</b>                                                     | <b>5</b> |

| 2.1. Verwendung der Zuwendung .....                                                       | 5        |

| 2.2. Die Wichtigsten Positionen des Zahlenmäßigen Nachweises .....                        | 5        |

| 2.3. Notwendigkeit und Angemessenheit der geleisteten Arbeit .....                        | 6        |

| 2.4. Verwertbarkeit des Ergebnisses im Sinne des fortgeschriebenen Verwertungsplans.....  | 6        |

| 2.5. Bekannt gewordener Fortschritt auf dem Gebiet des Vorhabens bei anderen Stellen..... | 6        |

| 2.6. Erfolgten oder geplanten Veröffentlichungen des Ergebnisses .....                    | 6        |

| <b>3. ERFOLGSKONTROLLBERICHT.....</b>                                                     | <b>7</b> |

| 3.1. Beitrag des Ergebnisses zu den Förderpolitischen Zielen.....                         | 7        |

| 3.2. Wissenschaftlich-technisches Ergebnis des Vorhabens .....                            | 7        |

| .....                                                                                     | 12       |

| 3.3. Fortschreibung des Verwertungsplans.....                                             | 14       |

| 3.4. Arbeiten, die zu keiner Lösung geführt haben .....                                   | 14       |

| 3.5. Präsentationsmöglichkeiten für mögliche Nutzer.....                                  | 14       |

| 3.6. Einhalten der Kosten- und Zeitplanung .....                                          | 15       |

| 3.6.1. Zeitplan.....                                                                      | 15       |

| 3.6.2. Ausgabenplan.....                                                                  | 15       |

## Angaben zu dem Zuwendungsempfänger

**Zuwendungsempfänger:** Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V.-Fraunhofer Institut für Zuverlässigkeit und Mikointegration IZM (IZM)

**Förderkennzeichen:** 13N14935

**Thema des Projektes:** Photonic Embedding of Active Region LASER Chips on Silicon

**Zuwendungsbescheid/Vertrag vom:** 05.04.2019

**Berichtszeitraum:** 01.05.2019 bis 31.10.2022

## 1. Kurzdarstellung

### 1.1. Aufgabenstellung

Die Zielstellung des Projekts ist gegenüber dem Antrag unverändert.

Das Fraunhofer IZM ist gemäß des Antrag im für Projekt die Durchführung fachlicher Projektarbeiten AP 5 verantwortlich gewesen und beteiligte sich in Spezifikations- und Designarbeiten in AP1. Hier wenden die elektrischen und mechanischen Randbedingungen für die späteren Arbeitspakte festgelegt. Der Schwerpunkt der Arbeit lag hier im Arbeitspaket AP5. Hier sollte die Bearbeitung von 200mm Substraten mit eingebetteten III-V Halbleiter und Si-Waveguidestrukturen bearbeitet werden. Es sollten eine geeignete Maskierung für das Öffnen von III-V Halbleiter entwickelt und ein hoch selektive Ätzprozesse für die Kontaktierung der eingebetteten QP-Lasers. Die Kontaktierung des Lasers erforderte die Entwicklung eines niederohmigen Übergangs zwischen Halbleiter und der Metallisierungslage. Dabei ist eine Anpassung der einzusetzenden Materialen für die spätere Funktion und Zuverlässigkeit des Systems entscheidend.

Im Arbeitspaket AP1 brachte sich das IZM in die Designentwicklung ein.

### 1.2. Voraussetzungen

Um das Ziel, durch die Erweiterung einer siliziumphotonischen EPIC Plattform um Quanten Punkt basiertes Indiumphosphid (InP) neuartige optische Transceivermodule für den Datenkommunikationsverkehr – speziell Datacenter Interconnects – zu entwickeln, die durch die direkte Integration von Lichtquellen auf Siliziumchips – neben im Vergleich zu heutigen Modulen eine gesteigerte Datenrate - einen kleineren Platzbedarf und eine deutlich erhöhte Kosteneffizienz aufweisen, waren neuartige Ansätze nicht nur in einzelnen Teilgebieten isoliert, sondern auch im Gesamtsystem erforderlich. Keine der beantragenden Firmen und Forschungseinrichtungen verfügte über ausreichende eigene Ressourcen und technologisches Wissen, um alleine die Projektziele zu entwickeln. Die Komplementarität der Partner aus dem Anwendungsbereich, der Halbleiterindustrie und innovativer KMUs und sowie erfahrener, akademischer Partner förderte die Schaffung einer Gesamtlösung, erzeugt aber die Notwendigkeit der Zuwendung, da ein derart großer Innovationsschritt nur in enger Kooperation gemeinsam unternommen werden kann.

### 1.3. Planung und Ablauf des Vorhabens

Gegenüber der Antragsplanung haben sich über die Projektlaufzeit keine wesentlichen Änderungen hinsichtlich der technologischen Realisierbarkeit des Forschungsvorhabens erarbeitet.

Zu Beginn des Projektes wurden Präsenztreffen organisiert und zusätzlich wurden Technologiemeetings abgehalten. Diese waren zum Projektbeginn in Präsenz, mussten jedoch im weiteren Projektverlauf auf Bilaterale und multilaterale Meetings umgestellt um die Ideen und Konzepte auszutauschen und die Vorarbeiten zu planen.

Als Vorarbeiten wurde die Herstellung von hochwertigen III/V Materialien in den Laboren der Konsortiums Partner definiert. Erste Entwicklungsarbeiten konnten am IZM durchgeführt werden, wurden mit den Konsortiums Partner geteilt und standen zum Projektende zur Verfügung. Dabei erfolgte die Koordinierung der Partner und Ergebnisse durch den Projektleiter in den abgehaltenen Technologiemeetings.

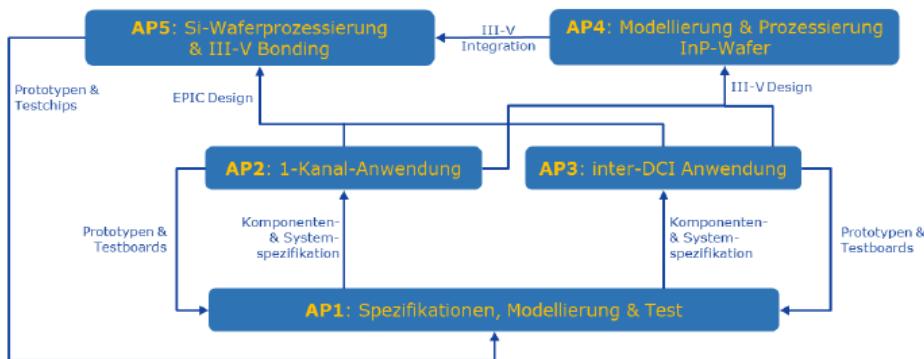

Die Arbeitspakete wie sie im Antrag im Abschnitt drei dargestellt wurden, sind bearbeitet worden. Abbildung 1 zeigt den geplanten Projektverlauf.

Abbildung 1 Schematische Darstellung der APs in diesem Projekt und deren Ablauf

#### 1.4. Wissenschaftlicher und technischer Stand

Der mit Abstand wohl größte Nachteil siliziumphotonischer Technologie gegenüber III-V basierter Halbleitertechnologie ist das Fehlen einer effizienten Lichtquelle. Daher ist es nicht verwunderlich, dass es weltweit mehrere Gruppen gibt, die sich mit Hybrid-Integration von III-V Lasern auf Si-Photonic-Chips beschäftigen, z.B. die Gruppen von J. Bowers (UCSB), R. Bhaets / Roelkens / Morthier (Uni Ghent, IMEC), III-V Labs/CEA-Leti (Paris + Grenoble), Alcatel-Lucent Bell-Labs (USA) und Y. Arakawa (Univ. of Tokyo), wobei sowohl "die"-Bonding als auch "Wafer"-bonding verwendet wird. Abbildung 3 zeigt einen Hybridaufbau, wie er von der UCSB-Gruppe realisiert wurde [2006-F]. Ein aktueller Überblick ist in Ref. [2015-D] und [2017-S].

Auf dieser Technologiebasis hatte die UCSB-Gruppe bereits eine im O-Band abstimmbare schmalbandige Lichtquelle realisiert mit Linienbreiten von unter 400 kHz (nur DFB laser) und unter 100 kHz mit zusätzlich gekoppelter externer Kavität integriert auf dem Si-Chip [2015-K]. Die Ghent-Gruppe hat kürzlich einen im C-Band abstimmbaren Ring-Laser durch eine vergleichbare Technologie realisiert [2017-Z], wobei die Linienbreite allerdings im Bereich von 1 MHz lag. Mit einem integrierten RSOA-Design und Ringresonatoren konnte die Gruppe von

Alcatel-Lucent Bell-Labs aber bereits Linienbreiten bis herab zu 2 kHz erzielt werden, wobei der Abstimmbereich einen Teil des C-Bandes entspricht [2014-D]. Die führenden Gruppen in der III-V Quantenpunkttechnologie sind auf GaAsbasierenden 1,3 µm Laser "QD-Laser/Uni Tokyo" (Japan), Innolume (Dortmund) und in Bezug auf monolithische Integration auf Si, die Gruppe Bowers (UCSB), Y. Arakawa (Uni Tokyo) und Liu / Seeds (University College London) [2017-N, 2017-C]. Mit "wafer-bonding" wurden auch erstmals bei Hewlett-Packard (Palo Alto) heterogen integrierte QD laser chips bei 1,3 µm realisiert [2017-Z]. Auf InP-basierenden 1,55 µm Laser sind aktuell III-V Lab (QDash Material) [2016-P] und die Universität Kassel (QP Material) führend. Die Uni Kassel hat Rekordwerte erzielt in der Temperaturstabilität des Schwellenstroms ( $T_0 > 140$  K), der Lichtleistung ( $T_1 > 900$  K) [2017-A, siehe Abbildung 3 (rechts)] und die höchste NRZ-Datenrate mit 35 GBit/s [2016-B], bzw. die geringste Linienbreite von QPQDFB-Lasern mit 110 kHz und integriert in einem InP-OEIC einen Abstimmbereich über das gesamte C+-Band [2017-B]. Eine hybride Integration von InP-basierten QP-Lasermaterial auf Si wurde bisher noch nicht durchgeführt und würde in diesem Projekt erstmals realisiert werden. Dies gilt sowohl für 1,3 µm als auch für 1,55 µm Wellenlänge. Aufgrund der intrinsischen Vorteile von QPStrukturen kann man bei gleichem Bauelementdesign eine wesentlich geringere Linienbreite erwarten (ca. 1 Größenordnung), höhere Temperaturstabilität, geringere Rückwirkungsempfindlichkeit und höhere Lebensdauern im Vergleich zu QW Lasern.

In dem Cluster „Digitalisierung, Industrie und Raumfahrt“ des Pfeilers 2 ist die quantenoptische Kommunikation als strategisch wichtiges Forschungsgebiet ausgewiesen. Für die Quantenkommunikation ist das vorhandene Glasfasernetz die bevorzugte Infrastruktur. Unter diesen Umständen ist eine On-Chip-Einzelphotonenquelle (SPS), die bei einem Fenster mit geringem Übertragungsverlust (1300-1600nm) und Raumtemperatur arbeitet, ein grundlegender Baustein für den Aufbau des enormen Quantennetzwerks. Es wurden für die Realisierung von SPS drei Hauptmaterialplattformen veröffentlicht - Diamant, Quantendots in 2D TMC (transition metal chalcogenides) und InAs/GaAs Quantendots.

## 1.5. Zusammenarbeit mit anderen Stellen

Dieser Punkt ist für das Projekt nichtzutreffend.

## 2. Eingehende Darstellung

### 2.1. Verwendung der Zuwendung

Die gewährte Zuwendung ist wie im Antrag unter Abschnitt 3 (Beschreibung des Arbeitsplans) beschrieben verwendet werden. Die detaillierte Zahlenmäßige Abrechnung ist separat zu diesem Bericht eingereicht worden.

### 2.2. Die Wichtigsten Positionen des Zahlenmäßigen Nachweises

In dem Rahmen des Projektes waren Personal- Reise und Materialkosten beantragt worden. Die beantragten und genehmigten Gelder wurden gemäß ihrer Bestimmung wie sie im Antrag

genannt wurden genutzt. Die Angefallenen Personalkosten betragen für den Berichtszeitraum €376.564,00. Die Materialkosten betragen für den gesamten Zeitraum €38.432,32.

### **2.3. Notwendigkeit und Angemessenheit der geleisteten Arbeit**

Um das Ziel, durch die Erweiterung einer siliziumphotonischen EPIC Plattform um Quanten Punkt basiertes Indiumphosphid (InP) neuartige optische Transceivermodule für den Datenkommunikationsverkehr – speziell Datacenter Interconnects – zu entwickeln, die durch die direkte Integration von Lichtquellen auf Siliziumchips - neben im Vergleich zu heutigen Modulen eine gesteigerte Datenrate - einen kleineren Platzbedarf und eine deutlich erhöhte Kosteneffizienz aufweisen, waren neuartige Ansätze nicht nur in einzelnen Teilgebieten isoliert, sondern auch im Gesamtsystem erforderlich.

In dem Projekt wurden die Arbeiten in Teilaspekten betrachtet. Dazu wurden jeweils die Arbeitspakete aufgeteilt und die Einzelprozesse zuvor an teilweise nicht funktionalen Mustern entwickelt. Die Muster wurden (wo möglich) direkt am IZM gefertigt, bzw. wurden von den Projektpartnern bereitgestellt. Hierbei war insbesondere das III/V Material, als Wafer aber auch als Coupons notwendig, um die Tests durchzuführen. Durch das Vorgehen, konnte Ressourceneffizient gearbeitet werden und Kosten vermieden werden.

### **2.4. Verwertbarkeit des Ergebnisses im Sinne des fortgeschriebenen Verwertungsplans**

Die ersten Ergebnisse konnten bereits mit industriellem Partner gezeigt werden und es wurden Projektideen besprochen, welche auf den hier entwickelt Ergebnissen basieren. Die Weiterverbreitung der Forschungsergebnisse durch das IZM dient der Verwertung der Projektergebnisse und ermöglicht damit auch den Zugang von Know-how für KMUs. Neben den direkten Kontakt mit potentiellen nationalen Partnern wurden auch bereits erste Ergebnisse veröffentlicht um auch einem weiteren Zugang zu ermöglichen. Es werden aktuell noch mindestens eine weitere Veröffentlichung mit dem Projektpartner IHP geplant.

### **2.5. Bekannt gewordener Fortschritt auf dem Gebiet des Vorhabens bei anderen Stellen**

Es gibt innerhalb des Projektzeitraums keine für das beschriebene Projektvorhaben relevanten Veröffentlichungen.

### **2.6. Erfolgten oder geplanten Veröffentlichungen des Ergebnisses**

Erste Ergebnisse sollen in internationalen Publikationen Fachpublikum veröffentlicht und präsentiert werden. Die Ergebnisse zu der Zuverlässigkeit der Metallisierung, welche Bestandteil der Arbeitspakete des IZM waren, sollen auf der Fachkonferenz Electronic Components and Technology Conference (ECTC) veröffentlicht werden.

Eine weitere Veröffentlichung zur technologischen Integration des Lasers gemeinsam mit dem Projektpartner IHP ist in Planung.

Die Ergebnisse werden in auch weiterhin in Netzwerken präsentiert – um neue Ideen für weitere Projekte in der Industrialisierung und neue Anwendungen zu sammeln sowie ausgeweitet zu werden.

### 3. Erfolgskontrollbericht

#### 3.1. Beitrag des Ergebnisses zu den Förderpolitischen Zielen

Über die Projektlaufzeit dieses Förderprojektes, wurde in Vorbereitung für die Einreichung des EU-Fördervorhabens ein enger Austausch der beteiligten Projektpartner erreicht, der auch über die Antragsphase bestehen bleibt. Der Ausarbeitung des Projektplans war eng verbunden mit der Vorstellung der eigenen Ideen, Vision hinsichtlich zukünftige Quantum Kommunikation und Quantum Sensorik und des Aufbaus eines deutschen, bzw. europäischen Quantennetzwerks.

#### 3.2. Wissenschaftlich-technisches Ergebnis des Vorhabens

Das Fraunhofer IZM arbeitete im Projekt PEARLS schwerpunktmäßig an Implementierung des Lasers notwendigen Prozessschritte wie III-V-Kontaktierung und der elektrischen Umverdrahtung, welche notwendig für die Technologieentwicklung zur Integration von III-V-Lasern sind.

Die wissenschaftlich technischen Ergebnisse wurden in den Zwischenberichten I-III detaillierter dargestellt und sollen hier kurz zusammengefasst dargestellt werden.

Ein erklärter Schwerpunkt des Projektes war es eine Wertschöpfungskette in Deutschland vom EPIC- und Laser-Design über die Prozessierung und Chipherstellung bis hin zur Aufbautechnik zu ermöglichen. Um dies zu adressieren wurden zunächst eine Spezifikation und Fertigungsplan erstellt. Dieser Plan berücksichtige zunächst lediglich die Fertigung der Wafer entlang der Institute. Abbildung 2 zeigt den sequentiellen Ablauf der Fertigung der Demonstratoren entlang der Institute. Dabei werden die an der Uni Kassel gewachsenen Coupons gesandt und dort auf die zuvor prozessierten Epic Wafer transferiert. Anschließend werden die Wafer ans IZM gesendet und ggf. nach der Prozessierung ein Rückversand ans IHP notwendig um letztendlich an der Universität Kassel geätzt und am final IZM metallisiert zu werden.

Abbildung 2: Waferfluss entlang der Institute

Dabei ist die Metallisierung und elektrische Kontaktierung eine Arbeitspaket des IZM. Hierzu wurden Metall Halbleiter Metallisierung sowohl für den p-Kontakt als auch für den n-Kontakt des III-V Wafermaterials zu entwickelt. Für die Entwicklung des niederohmigen Kontakts wurden eine Vielzahl an Metallierungen aus einer Literaturstudie betrachtet und ein für jeden Halbleiterkontakt eine Auswahl getroffen. Im Zwischenbericht I wurde eine detaillierte Tabelle (Tabelle 1) der möglichen Metallisierungssysteme für den III/V Halbleiterkontakt dargestellt. Im Verlauf des Projektes wurde sich für das Gold - Platin – Titan Metallisierungssystem entschieden, da es für beide Kontakte (p und n Kontakt) in Frage kommt und sehr niederohmige Kontakte ermöglicht. Zudem kann bei diesem Metallisierungssystem auf ein Annealing der Wafer verzichtet werden, was die Gefahren aufgrund der hohen Annealing Temperaturen vermeidet.

Für die Metallabscheidung wird am IZM PVD verwendet. Um die Kontakt zu p-GaAs aber auch die p-InP sind Targetmaterialien notwendig, die nicht am IZM vorhanden waren. Insbesondere musste Zink Target angeschafft werden um die Metallisierungssysteme Au/Zn/Au für p-GaAs und Au/Pd/Zn/Pd für InP zu realisieren und zu testen. Das Target wurde bestellt und ist nun am IZM vorhanden.

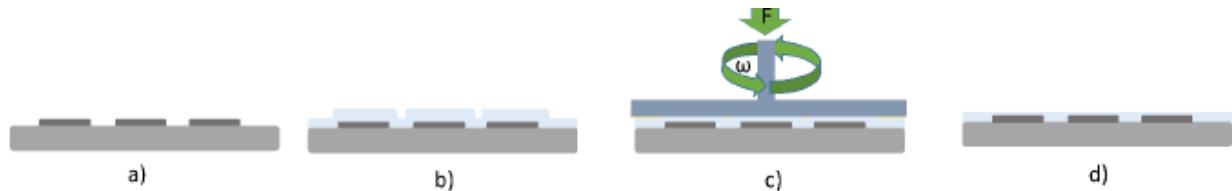

Damit die Bewertung des elektrischen Kontakts nicht an vollständig prozessierten EPIC Wafern mit transfergebondeten III-V Materialien durchgeführt werden musste, ist ein vorgezogener Test auf Testmaterial geplant, der zur Messung und Bewertung der Kontakte herangezogen wurde. Hierzu hat die Universität Kassel gemäß den geplanten finalen Schichten welche auf den EPIC Wafer transfergebondet werden auf Testmaterial abgeschieden und dem IZM zur Verfügung gestellt. Die Wafer wurden abgeschieden und liegen dem IZM vor. Die Wafergröße von 3" hat Einfluss auf Prozessierbarkeit am IZM, sodass für die Prozessierung spezielle Trägerwafer hergestellt werden müssen, damit sie von den Anlagen transportiert werden können. Hierzu wurden zwei Ansätze in Betracht gezogen: Das Herstellen eines Taschenwafers der eine Vertiefung in 3" Größe besitzen wo der III-V Wafer hineingelegt werden kann und so in der automatischen 200mm PVD Anlage transportiert werden kann. Die zweite Möglichkeit war ein temporäres Bondverfahren zu nutzen um den III-V Wafer auf einen 200mm Trägerwafer zu bonden. stellt die unterschiedlichen Trägertechnologien gegenüber. Während in Variante a) eine Vertiefung mittels DRIE in den Wafer geätzt werden muss, wird bei der Variante b) eine Polymerschicht auf einen Glaswafer aufgebracht und mittels Litographie strukturiert und anschließend mittels temporären Waferbonden der 3" Wafer aufgebracht.

Die zweite Variante ist in der Prozessführung deutlich aufwendiger, sichert jedoch bei der PVD Abscheidung einen besseren thermischen Kontakt zum Chuck während der Abscheidung. Die bei der Abscheidung der Metalle entstehenden Temperaturen müssen gemessen werden. Für die Arbeiten der elektrischen Test des Metall / Halbleiterkontakte wurde die zweite Variante verwendet um zu vermeiden, dass es zu einer undefinierten Aufheizung auf dem 3" Wafer

Abbildung 3: Gegenüberstellung der Trägertechnologien für die Prozessierung von 3" Wafermaterialien

kommt, welche gegenüber den EPIC Wafern sich unterscheiden würde und damit die Eigenschaften der Schicht unterschiedlich wären.

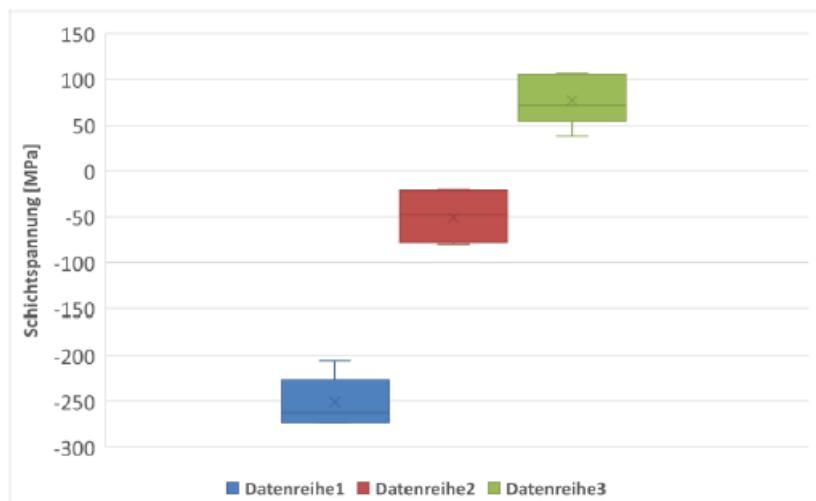

Die ausgewählte Metallisierungsschichtfolge Ti-Pt-Au wurde die Schichtspannungen während der Entwicklung des Prozesses dokumentiert und sind in Abbildung 5 dargestellt. Für eine hohe Zuverlässigkeit, muss der verwendete Schichtstapel eine möglichst geringe Gesamtspannung aufweisen. Daher müssen die Metalle und die verwendeten Schichtdicken aneinander angepasst werden.

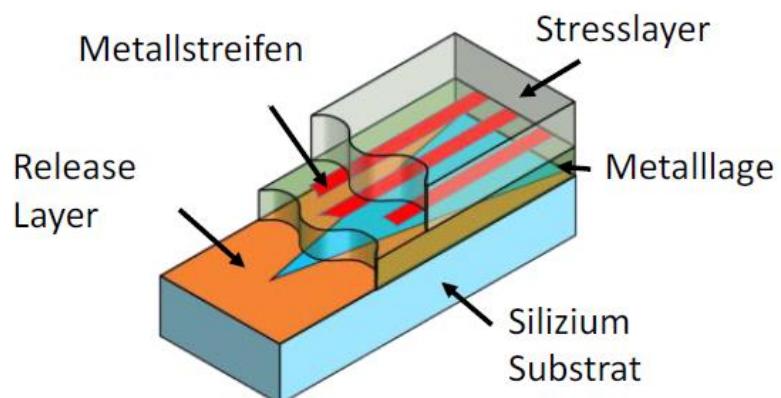

Die abgeschiedenen Metallschichten wurden auch hinsichtlich ihrer Haftung auf der Substratoberfläche untersucht. Hierzu wird der „Stripe Lift Off“ Test (SLT) verwendet. Der SLT erlaubt die Messung der Haftung bei Raumtemperatur. Aufgrund der Nutzung von intrinsischen Spannungen für eine Delamination, kann auf ein externes Messgerät für die Charakterisierung verzichtet werden. Als Ergebnis ermöglicht der SLT eine quantitative Charakterisierung der Haftung in Form der Bestimmung einer kritischen Energiefreisetzungsraten ( $J/m^2$ ). Die Energiefreisetzungsraten kann in eine Finite-Element-Simulation integriert werden und so die Grundlage für Zuverlässigkeitssprädiktionen liefern. Die Abbildung 5 zeigt schematisch den Aufbau des SLT Tests. Er besteht aus einer Releaselayer, welche auf einem Siliziumwafer aufgebracht wird und als Untergrund für unsere Haftungsuntersuchung der darauf abgeschiedenen Metalle verwendet wird. Die darüber aufgebrachten Metallstreifen (Kupfer) geben der Delamination eine Vorzugsrichtung wobei der Stresslayer (Polymer) die Kraft auf die Schicht ausübt und damit die Rissinitialisierung unterstützt.

Abbildung 4: Bestimmte Schichtspannungen für Titan in Abhängigkeit der Schichtdicke.

Mit dem Test konnten die entwickelten Metallisierungen hinsichtlich ihrer Haftung einfach bewertet und der Abscheideprozess entsprechend angepasst werden. Im Ergebnis dieser Tests wurden die Rücksputterparameter angepasst. Für das Rücksputtern wurde die Leistung erhöht und die Rücksputterzeit erhöht. Der Abtrag der Oxidschicht, welche sich auf dem Wafer befindet ist mit ca. 84nm deutlich höher als zunächst erhöft, jedoch kann dies einfach bei der Herstellung der Oxidschicht berücksichtigt werden und stellt keinerlei Problem bei der Prozessierung dar.

Abbildung 5: „Stripe Lift-Off“-Test (SLT) zur Haftungsmessung von dünnen Polymer- und Metallschichten

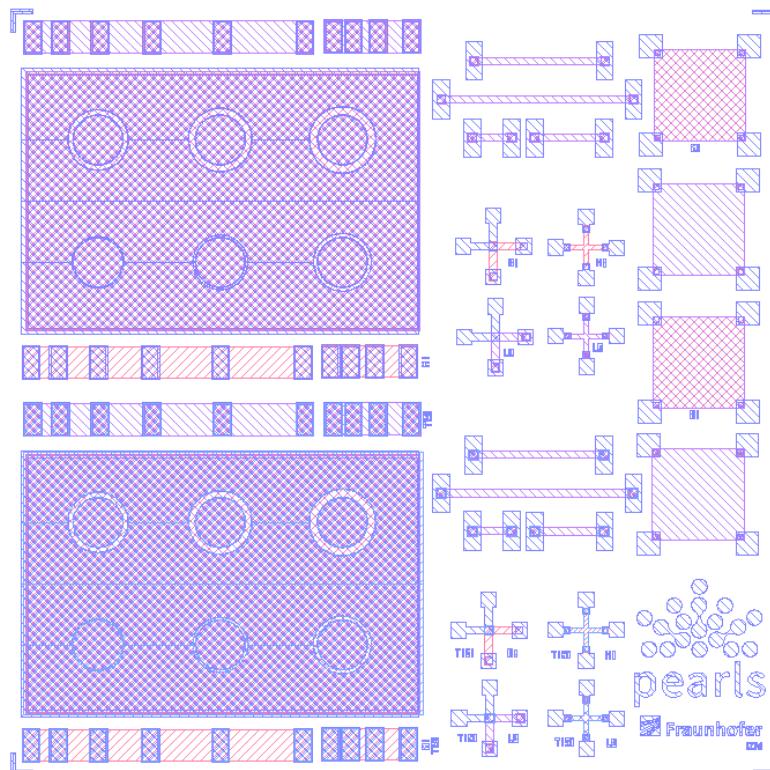

Für die elektrischen Tests wurde ein Testdesign erstellt, welches in Abbild 4 dargestellt ist. Es enthält unterschiedliche Strukturen, welche im Detail ebenfalls im Zwischenbericht I dokumentiert sind.

Abbildung 6: Elektrisches Testfelddesign für die Messung der Kontaktwiderstände zwischen III-V Halbleiter und Metallisierung

Um den Prozessfluss wie in Abbildung 1 dargestellt abbilden zu können, mussten am IZM Technologien zum planarisieren der eingebetteten III/V Chips entwickelt werden. Dies wurde insbesondere Notwendig, da die nachfolgende Lithographie zur Kontaktierung des Ridge auf dem III/V Laser sehr anspruchsvoll ist. Während die Lithographie am IHP vorhanden ist und musste diese am IZM noch entwickelt werden. Dies wurde notwendig, da aufgrund von durchgeführten Konterminationstest an am IZM prozessierten Wafern, Auffälligkeiten beobachtet wurden, die das Wiedereinschleusen der Wafer in den IHP Reinraum ausschlossen. Die Auflösung der am IZM vorhanden Maskaligner überschreitet die notwendige Auflösung, sodass auf ein Laser Direct Imaging System zurückgegriffen werden musste. Hierzu mussten Lacke evaluiert werden. Die zum Einsatz kommenden Lacke unterscheiden sich zu denen, die am Maskaligner verwendet werden. Daher musste ihre Anwendbarkeit für das Ätzen von Siliziumdioxid evaluiert werden. Die untersuchten Lacke würden in einer Schichtdicke von 0,7 bis 3 µm

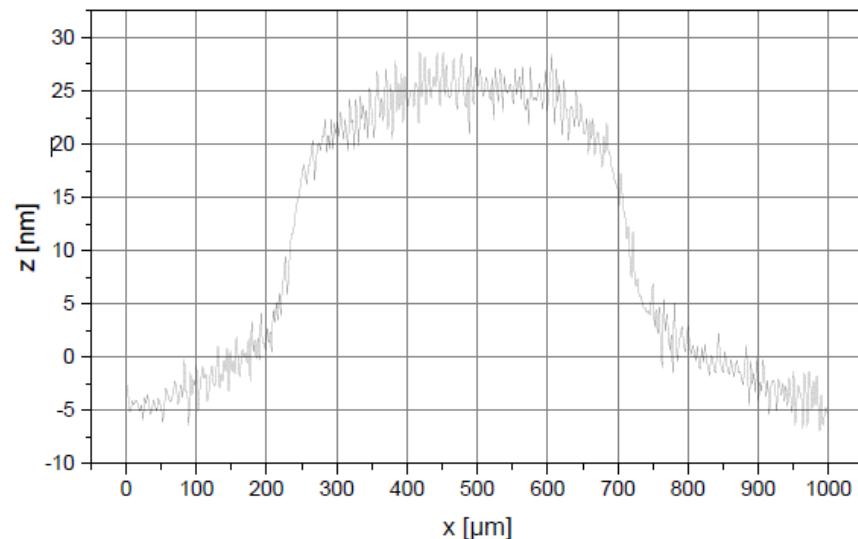

Der entwickelte Planarisierungsprozess ist in Abbildung 8 und die erreichten Ergebnisse in Abbildung 9 dargestellt. Man kann erkennen, dass die Erhebung im Bereich von 30nm liegt und damit für die nachfolgenden Lithographieprozesse keine Schwierigkeit darstellt.

Abbildung 7: Prozess zur Planarisierung des abgeschiedenen Oxides zur Ermöglichung der feinen Strukturen mittels Lithographie am IHP. a) Grundzustand nach dem Transferprint am IHP, b) Abscheidung der PECVD SiO<sub>2</sub> Schicht, c) Planarisieren der PECVD Schicht mittels CMP

Abbildung 8: Profil einer planarisierten Aluminiumteststruktur

Abbildung 9: Verlauf der Plasmareinigung des Transferprintingslacks

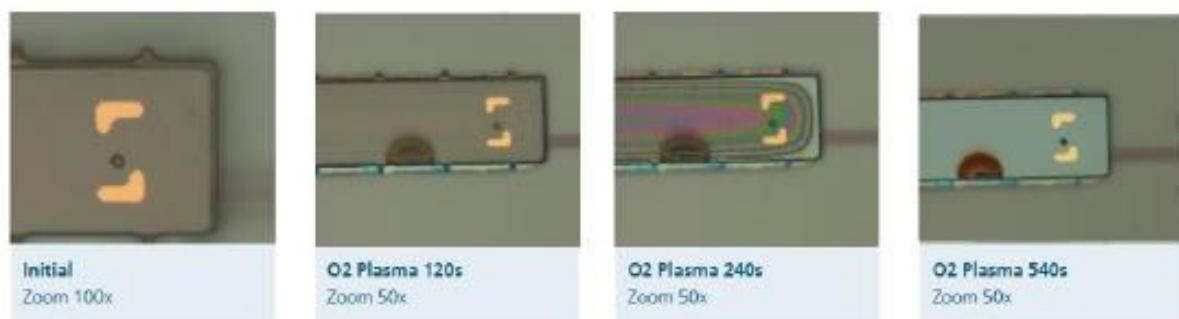

Für die Evaluierung des Prozessflows wurden Testwafer am IHP hergestellt und der Transferprozess für die III/V Chips entwickelt. Die für den Transfer verwendeten Lackstrukturen konnten jedoch nicht entfernt werden, sodass die Wafer mit Restlack ans IZM gesendet werden mussten. Zum Rückstandsfreien entfernen der Lackreste wurde ein starker RIE Prozess verwendet. Die Abbildung 9 zeigt die schrittweise Ätzung des Photolacks. Nach 540s waren nur noch vereinzelt kleine Lackreste zu erkennen. Um Reste auszuschließen,

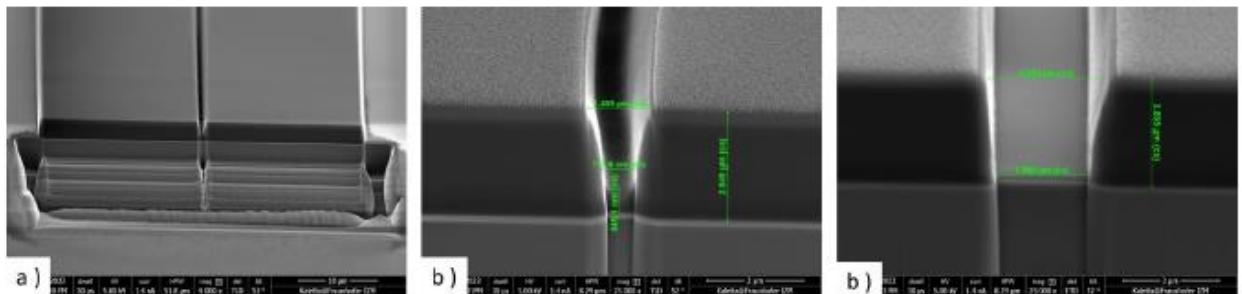

Abbildung 10: Ridge Struktur nach der photolithographischen Strukturierung und nach dem Ätzen des Oxides.

wurde anschließend noch 50% überätzt. Dabei wurden die Alignmentstrukturen auf den Chips nicht angegriffen, wie in dem rechten Bild erkennbar ist.

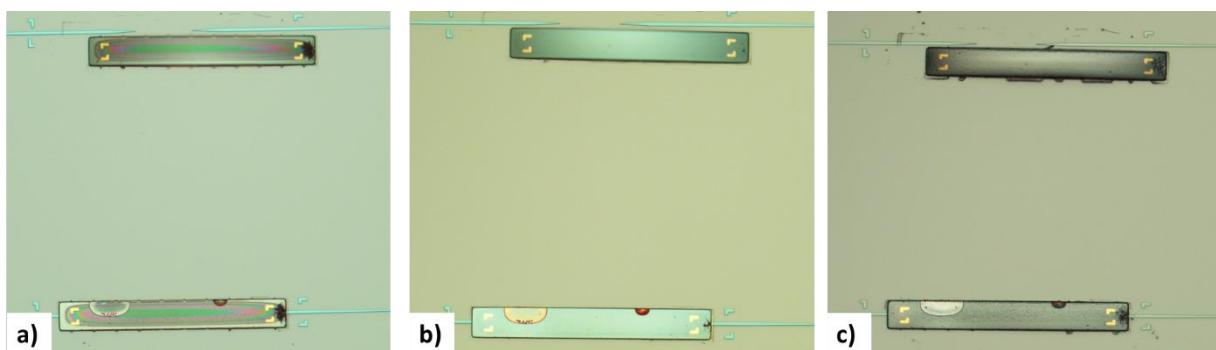

Die entwickelten Technologien wurden abschließend verwendet den Prozessfluss mit am IHP transfergebundenen Chips zu demonstrieren. Die Abbildung 11 zeigt eine Detailaufnahme zweier transferierten Chips mit Restlack nach dem Transfer am IHP (a), nach dem Lackreinigung (b) und nach der Oxidabscheidung (c).

Abbildung 11: Detailaufnahme zweier transferierten Chips mit Restlack nach dem Transfer am IHP (a), nach dem Lackreinigung (b) und nach der Oxidabscheidung (c).

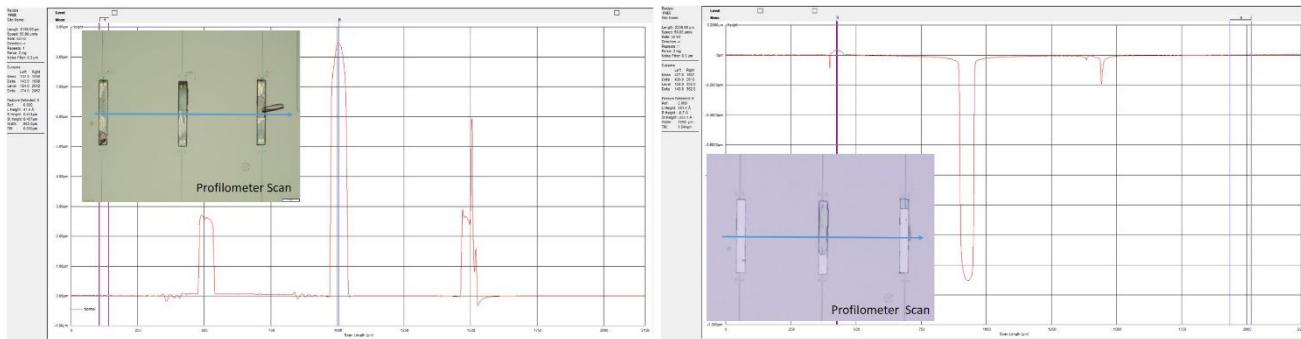

Abbildung 12: Profilometermessung der abgesetzten III/V Chips vor (links) und nach (rechts) dem Planarisierungsprozess

Abbildung 12 links zeigt die Messung der Stufenhöhe vor dem Planarisierungsprozess. Dabei betrug die gemessene Stufenhöhe der Höhe des abgesetzten Chips. Die Oxidabscheidung muss entsprechend mindestens der Höhe des Chips entsprechen damit über dem Chip planarisiert werden kann und noch zusätzlich genügend Oxid vorhanden ist, was als spätere Ätzmaske für das Strukturieren des Ridge. Auf der rechten Seite in der Abbildung 12 ist Prozess nach dem Planarisieren dargestellt.

Die entwickelten Technologien können verwendet werden um die Kontaktierung der III/V Substrate durchzuführen und ein funktionaler Laser herzustellen. Neben der Kontaktmetallisierung wird Aluminium eingesetzt um die Außenkontakte vorzunehmen. Alternativ ist auch eine Goldmetallisierung möglich. Die Entscheidung muss den angestrebten Aufbau und Verbindungstechnik die eingesetzt werden soll angepasst werden. In dem Projekt sind Drahtbond die einfachste Lösung um den Außenkontakt herzustellen.

Alle weiteren Aufbautechnologien sind am IZM als bereits entwickelte Standardprozesse verfügbar und bergen keine Entwicklungsaufwand, welcher in diesem Projekt abgebildet werden muss.

### 3.3. Fortschreibung des Verwertungsplans

In Rahmen des Projektes sind aufgrund der erzielten Ergebnisse neue Projektideen entwickelt worden. Diese wurden industriellen Partnern vorgestellt und gemeinsame Fortentwicklungen der hier erreichten Ergebnisse in bilateralen Projekten fortzuführen. Die Diskussionen sind nicht abgeschlossen und sollen fortgesetzt werden.

### 3.4. Arbeiten, die zu keiner Lösung geführt haben

Dieser Punkt ist für das Projekt nichtzutreffend.

### 3.5. Präsentationsmöglichkeiten für mögliche Nutzer

Im Rahmen der Konsortiums Findung in dem Projekt, wurden die Fähigkeiten der Beteiligen Partner hinreichend diskutiert und ausgetauscht. Im späteren Verlauf des Projektes, als das Forschungsvorhaben bereits sehr detailliert beschrieben werden konnte, wurde dieses an potentiellen Anwendern präsentiert. Zukünftig können vielleicht Teile der hier erarbeiteten

Ergebnisse zur weiteren Verbreitung noch in Fachpublikationen veröffentlicht werden um dies weiteren potentiellen Nutzer zugänglich zu machen.

### **3.6. Einhalten der Kosten- und Zeitplanung**

#### **3.6.1. Zeitplan**

Der Zeitplan des Projekts konnte nicht, wie im Projektantrag angegeben, eingehalten werden. Es gab eine 6-monatige Kostenneutrale Verlängerung. Der Antrag auf Verlängerung wurde genehmigt. Innerhalb der Verlängerung konnten die Verzögerungen durch Lieferung von neuen Wafern seitens der Projektpartner aufgearbeitet werden.

#### **3.6.2. Ausgabenplan**

Tabelle Übersicht stellt die geplanten und die abgerufenen Kosten des IZMs dar für den Zeitraum vom 01.05.2019 bis 31.10.2022 dar.

Zusätzlich konnten durch Einsatz von Webtelefonie (MS Teams, Webex, u.ä.) einige geplante Dienstreisen eingespart werden und die Abstimmungen online durchgeführt werden.

|         | Sachkosten | Personalkosten |

|---------|------------|----------------|

| Planung | 46.740,00  | 376.564,00     |

| Ist     | 38.432,32  | 391.798,56     |

Ein detaillierter Ausgabenplan wurde separat zum Abschlussbericht eingereicht.